@MrChips @Papabravo @ScottWang @DickCappels @Ian0 @ericgibbs @Bordodynov

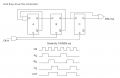

Hi all, I have stumbled across this circuit. Above is a frequency divider circuit (f/3 to be exact) quoted from here. I have tried to simulate it in LT Spice and followed exactly all the connections, but no output. I believe that the problem lies within the built-in logic gate by LT Spice. Can anyone spot any misconnections or problems here as I have even tried push-pull amplifier on the output of the logic gate since it outputs a maximum of 1V only which might be insufficient by the D pins as shown above?

Thank you for reading

Attachments

-

1.6 KB Views: 7