Hello all

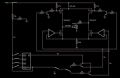

I'm trying to simulate a constant current circuit that will provide 100-600uA over a dynamic 1k-100k ohm load (which would mean a 60V source voltage). I've been playing with an OP Amp/MOSFET design in the circuit simulator from https://www.falstad.com. The pot and 10k simulate the dynamic load, the voltage feeding the 800k resistor is to simulate a 0-5V signal from a DAC. I think I have the correct values for the resistors now, but can someone confirm I am on the right track please? If possible, could someone shed light on the relevant math to figure out the resistor values (other than ohm's law ;-) )

Thank you in advance!

PS: Here is the code if anyone wants to have a look at it at falstad.com:

$ 1 0.000005 11.558428452718767 50 10 50 5e-11

f 384 208 432 208 0 0.1 0.02

w 352 32 352 48 1

g 432 432 432 464 0 0

R 352 32 352 0 0 0 40 60 0 0 0.5

a 192 208 288 208 9 15 -15 1000000 0.0005216453928277795 0.0005249343832020998 100000

r 432 304 432 432 0 1

r 384 208 288 208 0 10000

r 352 304 272 304 0 1000

w 192 224 192 304 0

w 352 304 432 304 0

w 432 304 432 224 0

w 192 304 272 304 0

w 432 144 432 192 0

174 352 48 400 144 1 90000 0.9851000000000001 LOAD

w 400 96 416 96 0

w 416 96 432 96 0

172 112 96 64 96 0 7 4.2 5 0 0 0.5 Voltage

r 144 96 144 192 0 800000

r 144 208 144 288 0 100

w 112 96 144 96 0

w 144 192 192 192 0

w 144 192 144 208 0

g 144 288 144 320 0 0

r 432 96 432 144 0 10000

I'm trying to simulate a constant current circuit that will provide 100-600uA over a dynamic 1k-100k ohm load (which would mean a 60V source voltage). I've been playing with an OP Amp/MOSFET design in the circuit simulator from https://www.falstad.com. The pot and 10k simulate the dynamic load, the voltage feeding the 800k resistor is to simulate a 0-5V signal from a DAC. I think I have the correct values for the resistors now, but can someone confirm I am on the right track please? If possible, could someone shed light on the relevant math to figure out the resistor values (other than ohm's law ;-) )

Thank you in advance!

PS: Here is the code if anyone wants to have a look at it at falstad.com:

$ 1 0.000005 11.558428452718767 50 10 50 5e-11

f 384 208 432 208 0 0.1 0.02

w 352 32 352 48 1

g 432 432 432 464 0 0

R 352 32 352 0 0 0 40 60 0 0 0.5

a 192 208 288 208 9 15 -15 1000000 0.0005216453928277795 0.0005249343832020998 100000

r 432 304 432 432 0 1

r 384 208 288 208 0 10000

r 352 304 272 304 0 1000

w 192 224 192 304 0

w 352 304 432 304 0

w 432 304 432 224 0

w 192 304 272 304 0

w 432 144 432 192 0

174 352 48 400 144 1 90000 0.9851000000000001 LOAD

w 400 96 416 96 0

w 416 96 432 96 0

172 112 96 64 96 0 7 4.2 5 0 0 0.5 Voltage

r 144 96 144 192 0 800000

r 144 208 144 288 0 100

w 112 96 144 96 0

w 144 192 192 192 0

w 144 192 144 208 0

g 144 288 144 320 0 0

r 432 96 432 144 0 10000

Attachments

-

23.5 KB Views: 1