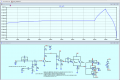

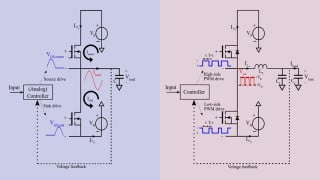

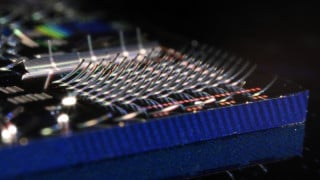

Hello,In the circuit below which LTSPICE file are attached. We have a Q1 transistor.

I was told about several methods to see if the PNP is under saturation

1.The Ic/Ib ratio which is HFE, but in the data sheet i det see what exact values are considered to be saturation and in what HFE it will be linear?

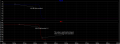

2.Vce plot shown below, again i am not sure what Vce says its saturated and what its linear because in the datasheet there are two cases2

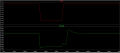

3.delay between the base and the collector voltages.How can i see In the datasheet the delay which will telll me that the delay is linear and when the delay says that my PNP is saturated?

Thanks.

https://www.mouser.com/datasheet/2/115/DIOD_S_A0011167377_1-2513105.pdf

I was told about several methods to see if the PNP is under saturation

1.The Ic/Ib ratio which is HFE, but in the data sheet i det see what exact values are considered to be saturation and in what HFE it will be linear?

2.Vce plot shown below, again i am not sure what Vce says its saturated and what its linear because in the datasheet there are two cases2

3.delay between the base and the collector voltages.How can i see In the datasheet the delay which will telll me that the delay is linear and when the delay says that my PNP is saturated?

Thanks.

https://www.mouser.com/datasheet/2/115/DIOD_S_A0011167377_1-2513105.pdf

Attachments

-

3.4 KB Views: 1

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin