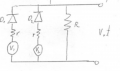

OR gate circuit- double voltage?

- Thread starter gbox

- Start date

Scroll to continue with content

AlbertHall

- Joined Jun 4, 2014

- 12,619

The output voltage cannot be more than the input voltages.

If V1 = V2 then

Vout = (V1 - Vdiode) * R/(R +r/2)

If V1 = V2 then

Vout = (V1 - Vdiode) * R/(R +r/2)

Sorry forgot KVL law for a momentThe output voltage cannot be more than the input voltages.

If V1 = V2 then

Vout = (V1 - Vdiode) * R/(R +r/2)

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin