What I'm trying to do?

I'm making a constant-current source based off an existing design. The specs of the existing design are:

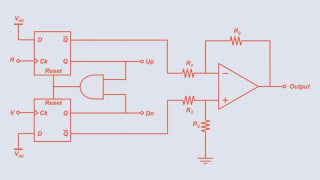

Existing Design

The design is of a constant current source capable of outputting 4-20mA output current from an input voltage of 0-2V.

The Problem

The problem is when physically making the circuit, the output of this circuit is stuck at 56mA irrespective of input.

I cannot find/contact the original author of the schematics to discuss the problem and its up to me to figure this out.

The simulations also show the same results as in reality:

Simulation Findings

Input: Sinusoidal Wave of 0-2V peaks of frequency 1 per second

Output Current: Constant current of 56 mA

Output Voltage: 13.6474V with small ripples with amplitude in microvolts.

Question

1) Where should I start looking for issues?

2) What is the name of the op-amp configuration being used in the second stage? I do know that the

first stage is a voltage follower.

I'm making a constant-current source based off an existing design. The specs of the existing design are:

Existing Design

The design is of a constant current source capable of outputting 4-20mA output current from an input voltage of 0-2V.

The Problem

The problem is when physically making the circuit, the output of this circuit is stuck at 56mA irrespective of input.

I cannot find/contact the original author of the schematics to discuss the problem and its up to me to figure this out.

The simulations also show the same results as in reality:

Simulation Findings

Input: Sinusoidal Wave of 0-2V peaks of frequency 1 per second

Output Current: Constant current of 56 mA

Output Voltage: 13.6474V with small ripples with amplitude in microvolts.

Question

1) Where should I start looking for issues?

2) What is the name of the op-amp configuration being used in the second stage? I do know that the

first stage is a voltage follower.

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin