Hi people,

It has been quite a long time since I posted anything lately

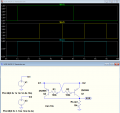

Refering to the XOR gate schematic and truth table above from here, I have designed them in LT Spice. Higlighted in green are the 2 inputs and purple is output.However, to my surprise, when A and B are both true (A=5V , B=5V in LT Spice) , it does not really get pull down to 0. Is this normal and are these circuits normally contain an op amp to set the threshold voltage to make it either on or off (1 or 0 only) ? I have attached my LT Spice below for your convenience

Thank you and have a nice day

Attachments

-

3.6 KB Views: 42