Why does IO devices doesn't need address bus? And why domes DMAC doesn't need data bus?

- Thread starter terabaaphoonmein

- Start date

Scroll to continue with content

Can you tell me the real diagram of this? This came from pretty reliable source, I am surprised that this is wrong.The diagram as it is presented is inaccurate. It cannot function correctly as it is drawn.

Sure, but I'd question the "reliable source" statement. That assertion is pure BS.Can you tell me the real diagram of this? This came from pretty reliable source, I am surprised that this is wrong.

The processor, memory, peripheral devices, AND the DMA Controller SHARE all of the address bus, data bus, and control signals.

You should think of the DMA controller as a 'substitute processor' while it is active. Therefore it must be able to run the exact same cycles as the processor.

The switches in the diagram are a polite fiction. In truth the DMA controller puts its bus drivers in a high impedance when the processor controls the bus. The processor does the same thing when the DMA controller controls the bus.

DickCappels

- Joined Aug 21, 2008

- 10,180

With memory-mapped I/O you do need an address bus and in most cases a data bus.

The type of I/O is irrelevant. You still need at least a portion of the address bus, the data bus, and the IO/M control signal, as well as RD* and WR*.With memory-mapped I/O you do need an address bus and in most cases a data bus.

I think that you are misinterpreting the diagrams (or the diagrams are badly drawn).

The arrows are not physical switches which would take too long to switch. They were meant to indicate where the signals are flowing.

The data bus is always connected to the CPU, memory, and I/O devices. Which devices actually use the data bus depends on the applicable control signals and the phase of the system clock. In DMA mode, data is exchanged between memory and I/O device, or I/O device and I/O device. When a device is not sending data to the data bus it goes into high-impedance state (which diagrammatically may be incorrectly drawn as a switch).

Similarly, in DMA mode, the address bus is accessed by the DMA controller, not the I/O device.

In memory-mapped I/O scheme, address bus is used by I/O address decoder and sent to I/O device as a single /CE signal or as /RD and /WR.

The arrows are not physical switches which would take too long to switch. They were meant to indicate where the signals are flowing.

The data bus is always connected to the CPU, memory, and I/O devices. Which devices actually use the data bus depends on the applicable control signals and the phase of the system clock. In DMA mode, data is exchanged between memory and I/O device, or I/O device and I/O device. When a device is not sending data to the data bus it goes into high-impedance state (which diagrammatically may be incorrectly drawn as a switch).

Similarly, in DMA mode, the address bus is accessed by the DMA controller, not the I/O device.

In memory-mapped I/O scheme, address bus is used by I/O address decoder and sent to I/O device as a single /CE signal or as /RD and /WR.

ronsimpson

- Joined Oct 7, 2019

- 3,037

There are different words to say the same thing. Some of this topic is just on word usage.

There are different types of "computers" example memory mapped IO verses IO mapped. Some computers have a bus what is both a Address and Data bus. Same wires but two functions divided by time. Some computers have buss for instructions and a totally different bus for data and a different slow speed but for IO.

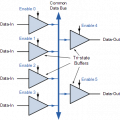

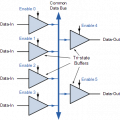

I think the switches are both right and wrong at the same time. Just to simply explain how thing work they are right but in practice they are not that way. The switches are really tristate buffers that allow many 'things' to drive a bus.

Years ago I worked on a custom IC for ST. I only did the IO area. The Address bus was across the top of the silicon while the data bus was on the bottom. All the functions were down the middle like what I drew. My block was slow and was on the far right side. Lets say the CPU was on the left, then DMA, Memory etc. All blocks had wires that reached into all the busses.

At one moment in time:

The CPU has the address for the next instruction ready to go onto the A-bus,

The DMA has 4 addresses one of which is ready to be pushed onto the A-bus.

All blocks have data ready to go onto the D-bus.

All busses are shared so only one block at a time can push data (or address) on a bus.

The word "switch" is problematic. Busses are more like tis picture. Thank you Google pictures. Here four "things" can push information onto this Common Bus and two can pull data off the bus. You could draw a 4-position switch but in reality there are 4-tristate buffers. Either way only 1 of 4 devices (at a time) can put data onto the bus.

There are different types of "computers" example memory mapped IO verses IO mapped. Some computers have a bus what is both a Address and Data bus. Same wires but two functions divided by time. Some computers have buss for instructions and a totally different bus for data and a different slow speed but for IO.

I think the switches are both right and wrong at the same time. Just to simply explain how thing work they are right but in practice they are not that way. The switches are really tristate buffers that allow many 'things' to drive a bus.

Years ago I worked on a custom IC for ST. I only did the IO area. The Address bus was across the top of the silicon while the data bus was on the bottom. All the functions were down the middle like what I drew. My block was slow and was on the far right side. Lets say the CPU was on the left, then DMA, Memory etc. All blocks had wires that reached into all the busses.

At one moment in time:

The CPU has the address for the next instruction ready to go onto the A-bus,

The DMA has 4 addresses one of which is ready to be pushed onto the A-bus.

All blocks have data ready to go onto the D-bus.

All busses are shared so only one block at a time can push data (or address) on a bus.

The word "switch" is problematic. Busses are more like tis picture. Thank you Google pictures. Here four "things" can push information onto this Common Bus and two can pull data off the bus. You could draw a 4-position switch but in reality there are 4-tristate buffers. Either way only 1 of 4 devices (at a time) can put data onto the bus.

You May Also Like

-

Duke University’s MadRadar Attack Causes Automotive Radar to ‘Hallucinate’

by Aaron Carman

-

Nordic, MediaTek, and U-blox Take on New Wireless Frontiers

by Jake Hertz

-

Infineon Leverages Coreless Transformer Design in Solid-State Isolators

by Jake Hertz

-

Introspect Technology Introduces LPDDR5/LPDDR5X Protocol Analyzer

by Duane Benson