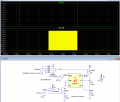

Hi. I have a PWM signal generator IC LTC6992-1 in my circuit, frequency of which is needed to be controlled by the DC source feeding the whole circuitry. In the schematic file the MOD input is set to be 0.5V to hinder confusion while commenting on frequency, normally it is desired to be dictated by the source as well. The 6990 model allows frequency control with voltage but with a constant %50 duty cycle fot the output. I need to control both so I also appreciate any solution that merges the two models somehow (Its even better considering the 6990 has an enable pin). Normally the frequency of the device is set by the three resistors R1 R2 and Rset. Frequency adjustment relies on the changes in Rset value so I came up with few ideas like using a potentiometer in series but that requires mechanical action rather than an internal voltage referencing. Using digital pots requires some controller circuitry so I had to give up on that too. Also, I dont have enough familiarity with FETs as well and I felt like operating them on the linear region precisely would demand lots of math on current and power limitations. As I got no other ideas on implying a continuous relation between the busbar voltage and the variable resistance I decided to set some modes and determine tresholds for each like first MOSFET is to be switched on when 40V is reached and it goes on with increments of 10 Volts for the other switches. To do so I thought of placing zeners between the gates of the MOSFETs and nodes with divided voltages but since they also allow voltages below 10 volts the switching tresholds are not as desired. How can I create this dependency in an analog or somewhat digital manner without using a considerable number of comparators and sources?

file updated*

file updated*

Attachments

-

3.4 KB Views: 7

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin