I recently fell on what appears to be a nice circuit, simple, using only a single NAND gate, a resistor and a cap. Unfortunately, the author of that circuit, Tony van Roon, is dead, so I cannot contact him to ask him my question. So I post my question here.

The circuit is available at http://circuitdiagram.net/wp-content/uploads/2011/01/clock-generator.jpg

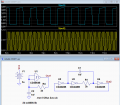

When I tried the circuit with an SN74LS00N from Texas Instruments, it seems that these chips to be too fast ( in the order of 200MHz ) and the clock signal never reaches 2.0V (which is the lower voltage for a High level, accordingly to the datasheet, and the signal appears sinusoidal (and not a succession of square pulses), even with a 1uF cap (film, not electrolytic) and a resistor of 5 MOhm.

While I am aware of other circuits to make a clock like signal, my question is about THIS circuit only. Am I right to think that the LS family is simply too fast to be somehow useful and that there is no real hope for this circuit with the 74LS00? Or there is a simple "cure" ?

The circuit is available at http://circuitdiagram.net/wp-content/uploads/2011/01/clock-generator.jpg

When I tried the circuit with an SN74LS00N from Texas Instruments, it seems that these chips to be too fast ( in the order of 200MHz ) and the clock signal never reaches 2.0V (which is the lower voltage for a High level, accordingly to the datasheet, and the signal appears sinusoidal (and not a succession of square pulses), even with a 1uF cap (film, not electrolytic) and a resistor of 5 MOhm.

While I am aware of other circuits to make a clock like signal, my question is about THIS circuit only. Am I right to think that the LS family is simply too fast to be somehow useful and that there is no real hope for this circuit with the 74LS00? Or there is a simple "cure" ?