Hello, There Is this great working PID system I am trying to understand its logic.I am trying to compare this circuit to the classic diagram of PID feedback system.

Two questions:

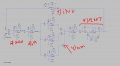

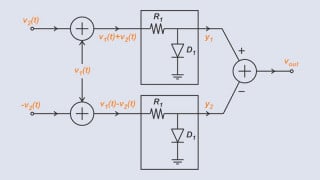

1. what is the analog logic of block I designates as 1,how can I analize its tranfer function?

2. Why are they inverting the output signal before going into PID?

https://github.com/HemakanthNatkuna...t/blob/main/EC5030_DesignProject_2020e050.pdf

Ltspice and photos are attached.

Two questions:

1. what is the analog logic of block I designates as 1,how can I analize its tranfer function?

2. Why are they inverting the output signal before going into PID?

https://github.com/HemakanthNatkuna...t/blob/main/EC5030_DesignProject_2020e050.pdf

Ltspice and photos are attached.

Attachments

-

8.9 KB Views: 6

-

61.2 KB Views: 13

-

51.3 KB Views: 12

-

149.1 KB Views: 8

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin