TX FIFO and RX FIFO in Network Controller

- Thread starter DragosAlbu

- Start date

Scroll to continue with content

But do you know how the parallel bits are taken from the bus and are put in the TX FIFO? Please if you can help me with this information.TX holds bits to be transmitted out.

RX holds received bits that need to be read by the device.

Both are temporary storages and not meant to be used to store important program data.

You know by reading the datasheet of the NIC controller chip.But do you know how the parallel bits are taken from the bus and are put in the TX FIFO? Please if you can help me with this information.

I believe the serialization of the parallel data in the TXFIFO takes place when the data is removed from the TXFIFO and placed into the TX SHIFT REGISTER. Similarly on receive the bytes(words) are assembled in a serial to parallel shift register and placed in the RXFIFO once the appropriate boundaries are recognized.

Do you know where can I find the datasheet of a simple NIC?You know by reading the datasheet of the NIC controller chip.

Do you know where can I find a better block diagram including the TX SHIFT REGISTER?I believe the serialization of the parallel data in the TXFIFO takes place when the data is removed from the TXFIFO and placed into the TX SHIFT REGISTER. Similarly on receive the bytes(words) are assembled in a serial to parallel shift register and placed in the RXFIFO once the appropriate boundaries are recognized.

How about a datasheet.Do you know where can I find a better block diagram including the TX SHIFT REGISTER?

Hello,

The following PDF will show you the ethernet theory of operation.

Bertus

The following PDF will show you the ethernet theory of operation.

Bertus

Attachments

-

388.5 KB Views: 32

Datasheet....where can I find that?How about a datasheet.

Thank you...but there's a lot of technical stuff for me....I'm studying Computer Science not Electronics....so I am trying to find something easier to understand.Hello,

The following PDF will show you the ethernet theory of operation.

Bertus

Hello,

In your other thread you shoed a slideshow anout the 82573L.

On this page you can find several documenents about this chip:

http://www.datasheetarchive.com/82573L-datasheet.html

Bertus

In your other thread you shoed a slideshow anout the 82573L.

On this page you can find several documenents about this chip:

http://www.datasheetarchive.com/82573L-datasheet.html

Bertus

Not to sugar coat this topic but you can't expect to dive into something of this complexity (run a marathon) without first learning to crawl and walk. So why don't you slow down, divide, and conquer.Thank you...but there's a lot of technical stuff for me....I'm studying Computer Science not Electronics....so I am trying to find something easier to understand.

Here are some datasheets for basic MSI parts:

http://www.nxp.com/documents/data_sheet/74HC_HCT164.pdf

http://www.nxp.com/documents/data_sheet/74HC_HCT166.pdf

http://www.nxp.com/documents/data_sheet/74HC_HCT166.pdf

The one with the serial output would be used in the transmitter. the one with the serial input would be used in the receiver. Notice how the serial ouput changes regardless of weather the register was "loaded" or "shifted". Here is a thought exercise:

If the data has to be shifted out LSB (Least Significant Bit) first -- how could you arrange for that to happen?

Deleted member 115935

- Joined Dec 31, 1969

- 0

small question, long answer ..

How much detail do you want ?

top level, ethernet is split into layers, as per the OSI model.

Layer 1 is the physical,

the cable and driving,

generally its considered they layer one is responsible for handling all the Ethernet electrical and ns by ns timing, and the interface to layer two is parallel,

i.e the layer one does the parallel to serial and back conversion and has the first / last fifos in.

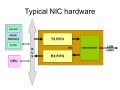

Having said that, the picture shows the fifos onto the cpu data bus,

Which implies the fifos are not at level 1, but higher up ,

The NIC does many things.

You could be suffering the old problem of students,

the answer depends not upon the question but what the question setter wants.

i.e. if you ask "why are days warmer then nights" to a phd student and to a 5 year old you would expect different answers.

How much detail do you want ?

top level, ethernet is split into layers, as per the OSI model.

Layer 1 is the physical,

the cable and driving,

generally its considered they layer one is responsible for handling all the Ethernet electrical and ns by ns timing, and the interface to layer two is parallel,

i.e the layer one does the parallel to serial and back conversion and has the first / last fifos in.

Having said that, the picture shows the fifos onto the cpu data bus,

Which implies the fifos are not at level 1, but higher up ,

The NIC does many things.

You could be suffering the old problem of students,

the answer depends not upon the question but what the question setter wants.

i.e. if you ask "why are days warmer then nights" to a phd student and to a 5 year old you would expect different answers.

FIFO, First In, First Out register array. Bytes are stuffed in one after another and read out in the same sequence. Check out a FIFO data sheet. 74LS224 for instance.Hey. I don't understand the difference between TX FIFO and RX FIFO inside the Network Interface Controller (Ethernet).View attachment 118279

You May Also Like

-

Intel Spins Off Altera as Independent FPGA Supplier

by Duane Benson

-

Building IoT Sensors Armed With AI, Wi-Fi 6, and Matter Capabilities

-

Nuvoton’s New Microprocessors Target Industrial HMI Applications

by Aaron Carman

-

Using a Raspberry Pi Pico to Enhance a Vintage Radio Shack Microcomputer Kit

by Don Wilcher