Hi,

This is a nagging problem with my version of a classic binary clock. It comes with all the baggage expected of an old project built with older tools, but here's what I have: My version of a design off the web uses 74393 counters to set up seconds, minutes and hours, with logic to clear each as appropriate and clock the next counter in the sequence. It works just fine until I try to implement the part that sets the minutes and hours. Here, it uses a debounced switch to enable the clock pulse to feed directly to the minutes counter input when pressed, without disconnecting that input from the output of the previous counter. A couple of diodes are supposed to take care of keeping the pulses positive coming from either output, and a resistor to ground pulls the input down if both outputs are low. Doesn't work. I'm confident counter B is counting, but when I put in the diode from its CLEAR over to C, the pulse isn't coming through. The min set module is working fine. When enabled, the minutes counter counts at 1 Hz. But nothing moves when set is not enabled.

Ideas about things that can be going wrong? My background is weak on theory, but I've dabbled for many years.

Note, I'm using LS393's, not HC393's.

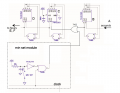

Attached is a piece of the schematic showing the B counter feeding the C counter, with the min set module also feeding the C counter. Other stuff cut out for simplicity.

Thanks for any thoughts. Tim

This is a nagging problem with my version of a classic binary clock. It comes with all the baggage expected of an old project built with older tools, but here's what I have: My version of a design off the web uses 74393 counters to set up seconds, minutes and hours, with logic to clear each as appropriate and clock the next counter in the sequence. It works just fine until I try to implement the part that sets the minutes and hours. Here, it uses a debounced switch to enable the clock pulse to feed directly to the minutes counter input when pressed, without disconnecting that input from the output of the previous counter. A couple of diodes are supposed to take care of keeping the pulses positive coming from either output, and a resistor to ground pulls the input down if both outputs are low. Doesn't work. I'm confident counter B is counting, but when I put in the diode from its CLEAR over to C, the pulse isn't coming through. The min set module is working fine. When enabled, the minutes counter counts at 1 Hz. But nothing moves when set is not enabled.

Ideas about things that can be going wrong? My background is weak on theory, but I've dabbled for many years.

Note, I'm using LS393's, not HC393's.

Attached is a piece of the schematic showing the B counter feeding the C counter, with the min set module also feeding the C counter. Other stuff cut out for simplicity.

Thanks for any thoughts. Tim

Attachments

-

193.4 KB Views: 29

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin