Simulating d flip-flops in LTspice issue

- Thread starter blahblah123456789

- Start date

-

- Tags

- d flip-flops ltspice

Scroll to continue with content

Thank you so much!hi blah,

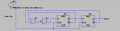

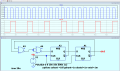

Add the options command line to the asc circuit.

Also set the Vcc voltages for the digital circuits

E

View attachment 343134

Thank you so much!

Actually just a follow up, would there be a way to make this circuit divide the freq by 3 as well as the duty cycle by 3hi blah,

Add the options command line to the asc circuit.

Also set the Vcc voltages for the digital circuits

E

View attachment 343134

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin