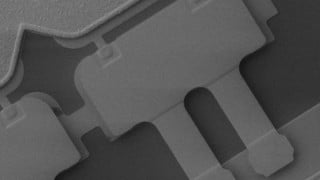

Hello! I am trying to design a differential 4-bit SAR ADC in Cadence, following the same structure as shown below (but for 4 bits):

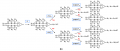

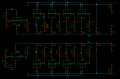

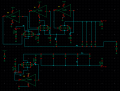

I am currently trying to simulate the CDAC stand-alone to ensure that I get the appropriate voltage values on the top plates of the capacitors, when I manually connect and disconnect the switches. My schematic looks like the following:

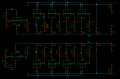

I have made two types of VerilogA switches, one with 1 n terminal, and another with 2 n terminals. The code is shown below:

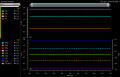

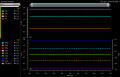

When running a 10us transient simulation in which I have the two input switches ON and the capacitor bottom plates connected to Vref through the switches, I get the simulation results shown below ( for Vip=1.3V and Vin=0.5V).

I believe these results make sense, but when I start trying to disconnect the switches so I can simulate the conversion cycle, I get a simulation error:

From my understanding, what I should expect to see is that whenever I turn the input switches OFF (disconnecting any input from the capacitor top plates), the top plates should be "floating" and change voltage value as the bottom plates of the capacitors get switched to ground (due to charge conservation).

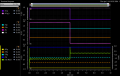

I don't know where I am making a mistake. I thought it could be the VerilogA switches that were not properly made, but when swapping these for transmission gates, the top plate of my capacitors don't seem to "float":

(Please note that I only used TG switches for both inputs (Vip and Vin) and for the MSB of the positive terminal (which uses two TG switches, one to Vref and one to ground)).

Any suggestion would be very much appreciated! Thank you for your help!

I am currently trying to simulate the CDAC stand-alone to ensure that I get the appropriate voltage values on the top plates of the capacitors, when I manually connect and disconnect the switches. My schematic looks like the following:

I have made two types of VerilogA switches, one with 1 n terminal, and another with 2 n terminals. The code is shown below:

When running a 10us transient simulation in which I have the two input switches ON and the capacitor bottom plates connected to Vref through the switches, I get the simulation results shown below ( for Vip=1.3V and Vin=0.5V).

I believe these results make sense, but when I start trying to disconnect the switches so I can simulate the conversion cycle, I get a simulation error:

From my understanding, what I should expect to see is that whenever I turn the input switches OFF (disconnecting any input from the capacitor top plates), the top plates should be "floating" and change voltage value as the bottom plates of the capacitors get switched to ground (due to charge conservation).

I don't know where I am making a mistake. I thought it could be the VerilogA switches that were not properly made, but when swapping these for transmission gates, the top plate of my capacitors don't seem to "float":

(Please note that I only used TG switches for both inputs (Vip and Vin) and for the MSB of the positive terminal (which uses two TG switches, one to Vref and one to ground)).

Any suggestion would be very much appreciated! Thank you for your help!

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin