Hi everyone,

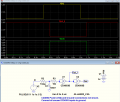

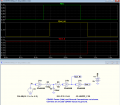

I have a project to make a delay block/ debouncer which has same function in LTC6994-2 with IC 555. I try to combine 2 ICs 555 monostable with a pulse from Astable Mode to detect the time delay of both rising and falling edge. However it does not work. Does anyone have a suggestion or idea for this schematic design.

The function of LTC6994-2: https://www.analog.com/media/en/technical-documentation/data-sheets/LTC6994-1-6994-2.pdf

Thanks in advance.

I have a project to make a delay block/ debouncer which has same function in LTC6994-2 with IC 555. I try to combine 2 ICs 555 monostable with a pulse from Astable Mode to detect the time delay of both rising and falling edge. However it does not work. Does anyone have a suggestion or idea for this schematic design.

The function of LTC6994-2: https://www.analog.com/media/en/technical-documentation/data-sheets/LTC6994-1-6994-2.pdf

Thanks in advance.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin