Is this interface circuit reliable?

- Thread starter Xavier Pacheco Paulino

- Start date

Scroll to continue with content

What are you trying to do? What current are you switching, what is the load?

if it is just switch a 24V load with a 5V signal, a logic level FET and a couple of resistors are all you need.

Is electrical isolation needed?

This may help...

https://forum.arduino.cc/index.php?topic=61308.0

if it is just switch a 24V load with a 5V signal, a logic level FET and a couple of resistors are all you need.

Is electrical isolation needed?

This may help...

https://forum.arduino.cc/index.php?topic=61308.0

MaxHeadRoom

- Joined Jul 18, 2013

- 30,581

Looks like a follow on of this post.

https://forum.allaboutcircuits.com/threads/active-high-vs-active-low-logic-optocouplers.147852/

I would also consider a mosfet, 2n7000 for e.g.

Max.

https://forum.allaboutcircuits.com/threads/active-high-vs-active-low-logic-optocouplers.147852/

I would also consider a mosfet, 2n7000 for e.g.

Max.

Yes, it's a follow. I just want to make sure if resistors values are okay for the design and if the circuit is reliable.Looks like a follow on of this post.

https://forum.allaboutcircuits.com/threads/active-high-vs-active-low-logic-optocouplers.147852/

I would also consider a mosfet, 2n7000 for e.g.

Max.

I need 24V to drive stepper motors drivers. They need 24V signal, so I need to convert my FPGA TTL output to that voltage levelWhat are you trying to do? What current are you switching, what is the load?

if it is just switch a 24V load with a 5V signal, a logic level FET and a couple of resistors are all you need.

Is electrical isolation needed?

This may help...

https://forum.arduino.cc/index.php?topic=61308.0

I will replace the 2n3904 with a MOSFET 2n7000.Looks like a follow on of this post.

https://forum.allaboutcircuits.com/threads/active-high-vs-active-low-logic-optocouplers.147852/

I would also consider a mosfet, 2n7000 for e.g.

Max.

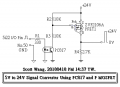

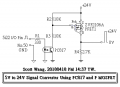

I have modified the design. Look at the picture attached in this post. Forget that LED for now. What do you think or suggest?

Attachments

-

18.9 KB Views: 17

You could make R4 a higher value. As it is, the max gate V you can get is 12V, not counting any drop across the opto.

The resistors make a voltage divider from 24V.

But 12V is more than likely quite ok.

The other thing I would change is the FET. The 2N7000 is really only ok for up to 400mA. I like BIG

I use a lot of BUK6207 FETs as I got them really cheap! A power logic level FET will be better for switching steppers than the one you have selected. For example...

https://www.sparkfun.com/products/10213

The resistors make a voltage divider from 24V.

But 12V is more than likely quite ok.

The other thing I would change is the FET. The 2N7000 is really only ok for up to 400mA. I like BIG

I use a lot of BUK6207 FETs as I got them really cheap! A power logic level FET will be better for switching steppers than the one you have selected. For example...

https://www.sparkfun.com/products/10213

Please don't try to use the low level as the active signal then it will occurs can't predictable result during the system at the initial time, the Vgs setup to close to 12V when the MOSFET is turn on.

The P MOSFET can be replaced by use a PNP as 2N2906, and the R2=4.7K, the values of R2 and R3 will affect the turn on time and the input frequency.

The P MOSFET can be replaced by use a PNP as 2N2906, and the R2=4.7K, the values of R2 and R3 will affect the turn on time and the input frequency.

"R2 and R3 will affect the turn on time and the input frequency", but will affect it drastically? Does it happen only if I use a PNP transistor? I don't want my parameters to be affected as I will driving steppers motors signals.Please don't try to use the low level as the active signal then it will occurs can't predictable result during the system at the initial time, the Vgs setup to close to 12V when the MOSFET is turn on.

The P MOSFET can be replaced by use a PNP as 2N2906, and the R2=4.7K, the values of R2 and R3 will affect the turn on time and the input frequency.

View attachment 150719

All the BJTs and MOSFETs will be affected by R2 and R3, you don't have to worry too much about that and you just need to set up the values to works, when it can't be works in any frequency and then you need to adjust the values, if the value more lower then the working frequency will be more higher, but the draw current will be more higher."R2 and R3 will affect the turn on time and the input frequency", but will affect it drastically? Does it happen only if I use a PNP transistor? I don't want my parameters to be affected as I will driving steppers motors signals.

How high of the frequency that you trying to use?

I'm not sure right now about the specific frequency. All I know for know is that frequency won't be higher than 100 kHz. You told me above not to try to use the low level as the active signal. That got my wires crossed because the tech support of the FPGA Card 5i22 (that I'm using), they told me not to use active high because it's not reliable and by using active low signal I guarantee outputs are off at startup from a hardware standpoint. Maybe he's wrong.All the BJTs and MOSFETs will be affected by R2 and R3, you don't have to worry too much about that and you just need to set up the values to works, when it can't be works in any frequency and then you need to adjust the values, if the value more lower then the working frequency will be more higher, but the draw current will be more higher.

How high of the frequency that you trying to use?

Let's back up.

Returning to the original circuit: It does need a base-emitter resistor on the transistor to prevent leakage current problems. If the output is to go to a signal input that requires just a small current, all the resistor values could be changed to reduce power consumption and improve long-term reliability.

"Maybe he's wrong." He is not wrong.

- Is the 24 volt signal going to drive the stepper motor directly or is it simply a signal input to an actual driver?

- Is there some data available on the driver if that is what is being used?

- If it is to drive the motors directly, what current is required?

- Mention has been made of 100 kHz. What is that for? Even a microstepping controller would not require anything that fast. There is no chance of getting 100 kHz through an ordinary coupler without access to the base of the photo transistor. There are suitable couplers.

- Is there a need for isolation? Isolation can be very useful in managing ground currents in some situations, but if it just for level shifting it isn't necessary.

Returning to the original circuit: It does need a base-emitter resistor on the transistor to prevent leakage current problems. If the output is to go to a signal input that requires just a small current, all the resistor values could be changed to reduce power consumption and improve long-term reliability.

"Maybe he's wrong." He is not wrong.

Last edited:

A lot depends on the processor you are going to use, and the port in question.

If the ports reset as inputs. a pull down resistor on a directly driven active high FET gate will keep it off. Or a pullup resistor on an active low output. So you need to find out what the pin in question defaults to on reset and use that as the off state. Active high or active low does not matter. Either is ok, as long as you design for the required state.

Another thing that may be worth incorperating in a harware watch dog that drops all drive or power to the motors if the processor hangs. The watchdog input comes from a processor pin that must be toggled regulaly to keep things working. I've used that sucessfully on products so everything defaults to off in a fault condition.

If the ports reset as inputs. a pull down resistor on a directly driven active high FET gate will keep it off. Or a pullup resistor on an active low output. So you need to find out what the pin in question defaults to on reset and use that as the off state. Active high or active low does not matter. Either is ok, as long as you design for the required state.

Another thing that may be worth incorperating in a harware watch dog that drops all drive or power to the motors if the processor hangs. The watchdog input comes from a processor pin that must be toggled regulaly to keep things working. I've used that sucessfully on products so everything defaults to off in a fault condition.

Last edited:

1. The 24V is simply a signal input to an actual driver. It's not going to drive the stepper directly.Let's back up.

- Is the 24 volt signal going to drive the stepper motor directly or is it simply a signal input to an actual driver?

- Is there some data available on the driver if that is what is being used?

- If it is to drive the motors directly, what current is required?

- Mention has been made of 100 kHz. What is that for? Even a microstepping controller would not require anything that fast. There is no chance of getting 100 kHz through an ordinary coupler without access to the base of the photo transistor. There are suitable couplers.

- Is there a need for isolation? Isolation can be very useful in managing ground currents in some situations, but if it just for level shifting it isn't necessary.

Returning to the original circuit: It does need a base-emitter resistor on the transistor to prevent leakage current problems. If the output is to go to a signal input that requires just a small current, all the resistor values could be changed to reduce power consumption and improve long-term reliability.

"Maybe he's wrong." He is not.wrong.

5. That's what I have to be clear if I need isolation. I don't have enough information about the stepper driver to determine if I need isolation. If isolation wouldn't be required I would just use a 74LS07 for level shifting.

So, if the 5i22 tech support is not wrong, I should then use active low input as recommended.

Using low level as input active signal was designed by the hardware of 5i22, so probably you can't change it.I'm not sure right now about the specific frequency. All I know for know is that frequency won't be higher than 100 kHz. You told me above not to try to use the low level as the active signal. That got my wires crossed because the tech support of the FPGA Card 5i22 (that I'm using), they told me not to use active high because it's not reliable and by using active low signal I guarantee outputs are off at startup from a hardware standpoint. Maybe he's wrong.

STARTUP I/O VOLTAGE

After power-up or system reset and before the the FPGA is configured, the pull-up resistors will pull all I/O signals to a high level. If the FPGA is used for motion control or controlling devices that could present a hazard when enabled, external circuitry should be designed so that this initial state results in a safe condition.

5i22 manual - The end of page 16.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin