Hello everyone, just a warning that this message is very long, and I hope it is clear enough, I am trying to put as much useful information as I can.

I am required to draw a timing signal diagram for a set of 5 instructions (described at the very bottom fo this post) that are programmed in an ATtiny2313A . I do not know how to do so, and would appreciate any help or guidance. I am lost as to what should my timing signal diagram should contain. I know it should contain a certain clock pulse, but which one, from the 555 timer directly? Or from one of the shift register output? (my report is due friday). What else should it contain? How should i draw it?

Information:

Two registers (register A and B) receive data from those instructions from the ATtiny2313A and the registers are 74ls173 chips each. They also take different combination of clock signal to output or input values to a bus which all devices are connected to. (will be explained below)

I have a drawing of my circuit, which does not have all the device completely connected. Because it was a previously done lab. I am still working on updating the diagram. (view file regAregB).

regAregB

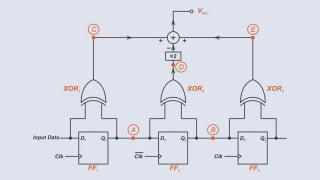

Also the clock is no directly added to the circuit. It has been done separately in another lab report. (view file timer555) Also the 555 is used for the timing signal generation, and connected to a shift register so that it can have its timing divided by 8 pulses. T0 would represent the first pulse connected to led 1, T1 represents the second pulse connected to led 2, and so on.

timer555

The timing signal diagram should be drawn according to an updated version of the circuit (which I dont have, I apologize, still updating it). Therefore. it should have Register A and Register B connected with their input/output enable as follow:

Output Enable for Register A: OEA = (T4 + Isig0) _ (T4 + Isig2)

Clock for Register A: CLKA = (T7 + Isig0) _ (T5 + Isig3)

Output Enable for Register B: OEB = (T4 + Isig1) _ (T4 + Isig3)

Clock for Register B: CLKB = (T7 + Isig1) _ (T5 + Isig2)

Output Enable for Sum Register: OESUM = (T6 + Isig0) _ (T6 + Isig1)

Clock for Sum Register: CLKSUM = (T5 + Isig0) _ (T5 + Isig1)

Note: Isig is the value outputted to the leds at the rightmost bottom of the circuit design. Where Isig0 would be the value at led0 , and Isig1 would be the value at led 1, so on and so forth.

The instructions are the following:

Inc B (instruction 1)

1. Data Register B outputs its contents onto the bus

2. SUM Register writes the incremented value of B = B + 1

3. SUM Register outputs value of B = B + 1 onto the bus

4. Data Register B writes the contents of the bus

Inc A (instruction 0)

1. Data Register B outputs its contents onto the bus

2. SUM Register writes the incremented value of B = B + 1

3. SUM Register outputs value of B = B + 1 onto the bus

4. Data Register B writes the contents of the bus

MovAB (instruction 2)

1. Data Register A outputs its contents onto the bus

2. Data Register B writes the contents of the bus

MovBA (instruction 3)

1. Data Register B outputting its contents onto the bus

2. Data Register A writing the contents of the bus

NOP (instruction 4)

NOP is short for no operation. This

instruction is simply a delay.

If you have read until this point, I thank you so much!!

I am required to draw a timing signal diagram for a set of 5 instructions (described at the very bottom fo this post) that are programmed in an ATtiny2313A . I do not know how to do so, and would appreciate any help or guidance. I am lost as to what should my timing signal diagram should contain. I know it should contain a certain clock pulse, but which one, from the 555 timer directly? Or from one of the shift register output? (my report is due friday). What else should it contain? How should i draw it?

Information:

Two registers (register A and B) receive data from those instructions from the ATtiny2313A and the registers are 74ls173 chips each. They also take different combination of clock signal to output or input values to a bus which all devices are connected to. (will be explained below)

I have a drawing of my circuit, which does not have all the device completely connected. Because it was a previously done lab. I am still working on updating the diagram. (view file regAregB).

regAregB

Also the clock is no directly added to the circuit. It has been done separately in another lab report. (view file timer555) Also the 555 is used for the timing signal generation, and connected to a shift register so that it can have its timing divided by 8 pulses. T0 would represent the first pulse connected to led 1, T1 represents the second pulse connected to led 2, and so on.

timer555

The timing signal diagram should be drawn according to an updated version of the circuit (which I dont have, I apologize, still updating it). Therefore. it should have Register A and Register B connected with their input/output enable as follow:

Output Enable for Register A: OEA = (T4 + Isig0) _ (T4 + Isig2)

Clock for Register A: CLKA = (T7 + Isig0) _ (T5 + Isig3)

Output Enable for Register B: OEB = (T4 + Isig1) _ (T4 + Isig3)

Clock for Register B: CLKB = (T7 + Isig1) _ (T5 + Isig2)

Output Enable for Sum Register: OESUM = (T6 + Isig0) _ (T6 + Isig1)

Clock for Sum Register: CLKSUM = (T5 + Isig0) _ (T5 + Isig1)

Note: Isig is the value outputted to the leds at the rightmost bottom of the circuit design. Where Isig0 would be the value at led0 , and Isig1 would be the value at led 1, so on and so forth.

The instructions are the following:

Inc B (instruction 1)

1. Data Register B outputs its contents onto the bus

2. SUM Register writes the incremented value of B = B + 1

3. SUM Register outputs value of B = B + 1 onto the bus

4. Data Register B writes the contents of the bus

Inc A (instruction 0)

1. Data Register B outputs its contents onto the bus

2. SUM Register writes the incremented value of B = B + 1

3. SUM Register outputs value of B = B + 1 onto the bus

4. Data Register B writes the contents of the bus

MovAB (instruction 2)

1. Data Register A outputs its contents onto the bus

2. Data Register B writes the contents of the bus

MovBA (instruction 3)

1. Data Register B outputting its contents onto the bus

2. Data Register A writing the contents of the bus

NOP (instruction 4)

NOP is short for no operation. This

instruction is simply a delay.

If you have read until this point, I thank you so much!!

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin