Kind friends

Please know that the following is an attempt to understand (as opposed to 'critique') the 'ways of Spice' -- I assure you this is utterly without 'attitude'! I approach this matter (and any responses) in an open, receptive and, most of all, grateful state of mind!

So... Here's the deal:

In an attempt to garner some measure of 'Spice proficiency' I have attempted to simulate a rather simple, familiar, 'tried and true' real world circuit -- with disappointing results

Real-world operation:

On power-up the 'real world' circuit's output EMF rises to a ≈ 110% 'overshoot' from which it recovers (within 50ms) to a highly stable, low noise (< 3mV) output -- Said noise being, as it is, characterized by the frequency of the oscillator - and, hence, merely 'ripple' - as opposed to 'regulation artifacts'...

Simulation:

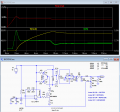

The simulation's output rises to a ≈ 140% overshoot thence, following > 200ms 'recovery' time, 'breaks into' a train of ≈90V(p-p) 'rebound pulses' asymmetrically superimposed on a the DC output (≈ E{selected})

I find it especially curious that (with reference to each 'rebound cycle') the 'correction' comes 'late' (≈ 10V below E{selected}) and with marked rapidity (≈800us)... --- Perhaps I am merely witnessing the analog nature of reality in collision with the digital 'mechanism' of Spice?

Please note: that although LtSpice's rather limited component library compelled my drafting of the simulation with 'ideal' and otherwise 'missapplied' components, I have, following close examination of simulator behaviour, found the simulation of said components to 'jibe' with those applied to the 'real-world' circuit... - moreover, with the possible exception of the op-amp, said substitutions could not produce the erroneous results seen in the simulation (i.e. "undamped hunting")...

For convenience of the readers I have included a screen capture of the simulation as well as the LtSpice schematic file for the circuit in question...

Many, many advance thanks for any insight, assistance or alternate points of view!

Very best regards

HP

PS -- FWIW The semiconductors used in the actual circuit are documented in bold blue text on the .asc file and screen capture...

Please know that the following is an attempt to understand (as opposed to 'critique') the 'ways of Spice' -- I assure you this is utterly without 'attitude'! I approach this matter (and any responses) in an open, receptive and, most of all, grateful state of mind!

So... Here's the deal:

In an attempt to garner some measure of 'Spice proficiency' I have attempted to simulate a rather simple, familiar, 'tried and true' real world circuit -- with disappointing results

Real-world operation:

On power-up the 'real world' circuit's output EMF rises to a ≈ 110% 'overshoot' from which it recovers (within 50ms) to a highly stable, low noise (< 3mV) output -- Said noise being, as it is, characterized by the frequency of the oscillator - and, hence, merely 'ripple' - as opposed to 'regulation artifacts'...

Simulation:

The simulation's output rises to a ≈ 140% overshoot thence, following > 200ms 'recovery' time, 'breaks into' a train of ≈90V(p-p) 'rebound pulses' asymmetrically superimposed on a the DC output (≈ E{selected})

I find it especially curious that (with reference to each 'rebound cycle') the 'correction' comes 'late' (≈ 10V below E{selected}) and with marked rapidity (≈800us)... --- Perhaps I am merely witnessing the analog nature of reality in collision with the digital 'mechanism' of Spice?

Please note: that although LtSpice's rather limited component library compelled my drafting of the simulation with 'ideal' and otherwise 'missapplied' components, I have, following close examination of simulator behaviour, found the simulation of said components to 'jibe' with those applied to the 'real-world' circuit... - moreover, with the possible exception of the op-amp, said substitutions could not produce the erroneous results seen in the simulation (i.e. "undamped hunting")...

For convenience of the readers I have included a screen capture of the simulation as well as the LtSpice schematic file for the circuit in question...

Many, many advance thanks for any insight, assistance or alternate points of view!

Very best regards

HP

PS -- FWIW The semiconductors used in the actual circuit are documented in bold blue text on the .asc file and screen capture...

Attachments

-

4.5 KB Views: 18

Last edited: