I've been playing around with a couple of NE555 PWM circuits in an effort to create a LED dimming solution (indicator and backlight) to include in an audio output switching circuit (like an A/B box).

The goal is the widest possible duty-cycle range -- from nearly 0% off to nearly 100% on -- at the lowest possible frequency that is relatively stable and appears flicker-free to both human eyes and common cameras.

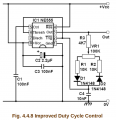

The best results I've generated so far have been from the circuit below but omitting R1, R2, and R3 and simply swapping C4 to get an acceptable frequency.

The circuit was lifted from the oscillators module at learnabout-electronics.org.

Is it safe to omit R1, R2, and R3? Or, do they serve a purpose beyond timing the charge/discharge cycle of C4?

If it matters, the output will be hitting the gate of a N-channel MOSFET set up as a low-side switch. I'm currently using a BS170 as it has the highest current-handling capability among the parts I have on hand. Recommendations for a similar part with a higher current-handling capability would not go unappreciated (1A? Maybe 2A?) as the number of LEDs I'll be driving with this circuit is variable.

Thanks!

The goal is the widest possible duty-cycle range -- from nearly 0% off to nearly 100% on -- at the lowest possible frequency that is relatively stable and appears flicker-free to both human eyes and common cameras.

The best results I've generated so far have been from the circuit below but omitting R1, R2, and R3 and simply swapping C4 to get an acceptable frequency.

The circuit was lifted from the oscillators module at learnabout-electronics.org.

Is it safe to omit R1, R2, and R3? Or, do they serve a purpose beyond timing the charge/discharge cycle of C4?

If it matters, the output will be hitting the gate of a N-channel MOSFET set up as a low-side switch. I'm currently using a BS170 as it has the highest current-handling capability among the parts I have on hand. Recommendations for a similar part with a higher current-handling capability would not go unappreciated (1A? Maybe 2A?) as the number of LEDs I'll be driving with this circuit is variable.

Thanks!

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin