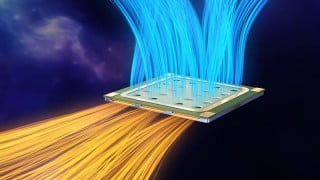

SPI trace length < 9mm

SPI trace length < 9mmSPI Via size 0.3mm x 0.6mm

Stitching Ground Via Size 0.2mm x 0.4mm

I'm estimating .5ns or 500ps rise time

Frequency estimate 2-3 GHZ

I did the best I can I don't know if there is something I could be doing better.

I would like to reduce noise as much as possible.

very sensitive EEG signal electrode traces 10H distance away. 10H = 10x distance from spi trace to ground plane.

I heard Rick Hartley say 20H was necessary

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin