Dear all,

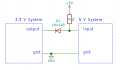

I need to convert the output of my 3.3V GPIO pin to a 5V signal. I am connecting the 5V output directly to the input of a CCD sensor. In total I have 6 timing signals that have to be sent out to from the FPGA to the sensor and all of them have to be converted from 3.3V to 5V. The frequency of these signal are very high as 1 signal has a 50% duty cycle at 12.5MHz. Another signal has a frequency of 12.5MHz with a 25% duty cycle. These are the fastest signals that have to be converted. In general i would like to keep the originality of the signal as much as possible with as little noise as possible. I was thinking of MOSFETS with dedicated MOSFET drivers(because the current from my FPGA is only 8mA) or CMOS to TTL converters. Does anyone have any suggestions on some good components or perhaps other ways to achieve this voltage amplification?

I have attached the signal below for better clarity, if I didn't mention something feel free to ask.

I need to convert the output of my 3.3V GPIO pin to a 5V signal. I am connecting the 5V output directly to the input of a CCD sensor. In total I have 6 timing signals that have to be sent out to from the FPGA to the sensor and all of them have to be converted from 3.3V to 5V. The frequency of these signal are very high as 1 signal has a 50% duty cycle at 12.5MHz. Another signal has a frequency of 12.5MHz with a 25% duty cycle. These are the fastest signals that have to be converted. In general i would like to keep the originality of the signal as much as possible with as little noise as possible. I was thinking of MOSFETS with dedicated MOSFET drivers(because the current from my FPGA is only 8mA) or CMOS to TTL converters. Does anyone have any suggestions on some good components or perhaps other ways to achieve this voltage amplification?

I have attached the signal below for better clarity, if I didn't mention something feel free to ask.

Attachments

-

95.9 KB Views: 9

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin