2N5457 spice model

- Thread starter cktboy

- Start date

Scroll to continue with content

Bordodynov

- Joined May 20, 2015

- 3,430

What were you using as a reference to compare the models with?found some but they are not accurate which I tested in Proteus.

Edit: And what inaccuracies did you identify?

Last edited:

hi ckt,

Is this the Model you have tried.?

What errors did you find.?

E

.MODEL J2N5457 NJF(Beta=1.125m Betatce=-500m Rd=1 Rs=1 Lambda=2.3m Vto=-1.372 Vtotc=-2.5m Is=181.3f Isr=1.747p N=1 Nr=2 Xti=3 Alpha=2.543u Vk=152.2 Cgd=4p M=311.4m Pb=500m Fc=500m Cgs=4.627p Kf=1.045e-002f Af=1)

Is this the Model you have tried.?

What errors did you find.?

E

.MODEL J2N5457 NJF(Beta=1.125m Betatce=-500m Rd=1 Rs=1 Lambda=2.3m Vto=-1.372 Vtotc=-2.5m Is=181.3f Isr=1.747p N=1 Nr=2 Xti=3 Alpha=2.543u Vk=152.2 Cgd=4p M=311.4m Pb=500m Fc=500m Cgs=4.627p Kf=1.045e-002f Af=1)

If you are claiming a model is inaccurate, you should present some evidence of the inaccuracy(s) so the developer can correct it.Hello,

Does anybody have a spice model for 2N5457 JFET? I have been searching online, found some but they are not accurate which I tested in Proteus.

Thanks

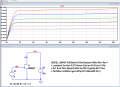

@ericgibbs, this is the same model as provided by @Bordodynov. The drain curve in proteus for this model is shown below.

This model shows that, for Vgs=0V the Idd is 400uA and Vp=1.9V but the minimum value of Idds is 1mA(datasheet: https://global.oup.com/us/companion...icrocircuits/students/mos/2n5457-motorola.pdf).

while I understand that the spice model may not always be accurate and that there is wide spread of electrical characteristics in the same transistors due to manufacturing process, I still think that the model is not within acceptable level. but this is my view, the model could be correct so I was looking for more spice model to experiment.

This model shows that, for Vgs=0V the Idd is 400uA and Vp=1.9V but the minimum value of Idds is 1mA(datasheet: https://global.oup.com/us/companion...icrocircuits/students/mos/2n5457-motorola.pdf).

while I understand that the spice model may not always be accurate and that there is wide spread of electrical characteristics in the same transistors due to manufacturing process, I still think that the model is not within acceptable level. but this is my view, the model could be correct so I was looking for more spice model to experiment.

@ericgibbs, this is the same model as provided by @Bordodynov. The drain curve in proteus for this model is shown below.

View attachment 256668

This model shows that, for Vgs=0V the Idd is 400uA and Vp=1.9V but the minimum value of Idds is 1mA(datasheet: https://global.oup.com/us/companion...icrocircuits/students/mos/2n5457-motorola.pdf).

previously i searched and found model in following links:

https://www.diyaudio.com/community/threads/pspice-for-2n5457.230743/

https://groups.google.com/g/sci.electronics.basics/c/TuYZGN3Tb2g?pli=1

while I understand that the spice model may not always be accurate and that there is wide spread of electrical characteristics in the same transistors due to manufacturing process, I still think that the model is not within acceptable level. but this is my view, the model could be correct so I was looking for more spice model to experiment.

That spec is with Vds = 15V. Did your simulation have that?@ericgibbs, this is the same model as provided by @Bordodynov. The drain curve in proteus for this model is shown below.

View attachment 256668

This model shows that, for Vgs=0V the Idd is 400uA and Vp=1.9V but the minimum value of Idds is 1mA(datasheet: https://global.oup.com/us/companion...icrocircuits/students/mos/2n5457-motorola.pdf).

while I understand that the spice model may not always be accurate and that there is wide spread of electrical characteristics in the same transistors due to manufacturing process, I still think that the model is not within acceptable level. but this is my view, the model could be correct so I was looking for more spice model to experiment.

Bob

Try this one.@ericgibbs, this is the same model as provided by @Bordodynov. The drain curve in proteus for this model is shown below.

View attachment 256668

This model shows that, for Vgs=0V the Idd is 400uA and Vp=1.9V but the minimum value of Idds is 1mA(datasheet: https://global.oup.com/us/companion...icrocircuits/students/mos/2n5457-motorola.pdf).

while I understand that the spice model may not always be accurate and that there is wide spread of electrical characteristics in the same transistors due to manufacturing process, I still think that the model is not within acceptable level. but this is my view, the model could be correct so I was looking for more spice model to experiment.

.MODEL J2N5457 NJF(Beta=0.150m Betatce=-500m Rd=1 Rs=1

+ Lambda=2.3m Vto=-2.572 Vtotc=-2.5m Is=181.3f Isr=1.747p

+ N=1 Nr=2 Xti=3 Alpha=2.543u Vk=152.2 Cgd=4p M=311.4m

+ Pb=500m Fc=500m Cgs=4.627p Kf=1.045e-002f Af=1)

Which model statement did you use?hmm if the spice model is good then it looks like there is something wrong with my drain plot in proteus but cannot find the reason. I have set the following in properties for dc transfer characteristics curve.

View attachment 256701

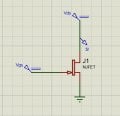

and the probes on the circuit for drawing drain curve is,

View attachment 256703

So what am I doing wrong?

The VGS stepping should be from 0v -1v

it is the same even with VGS stepping from 0V to -1V as shown below.Which model statement did you use?

The VGS stepping should be from 0v -1v

the curve is not visible as it is in order of micro amperes as shown in the previous graph

and here is how to draw drain curve in proteus:

what could be the problem? any suggestions?

Attachments

-

1,000 bytes Views: 10

@ericgibbs, yes the model seems good but in proteus i am not able to plot the graph correctly as shown in above

hi ckt,

I have one query ref your image, are you sure of the vertical scaling, it uses 'm' which indicates milliamps .

If that is correct, the first plot shows 0 to 11mA scaling,? Post #11

So the plots are around 0.5mA

E

I have one query ref your image, are you sure of the vertical scaling, it uses 'm' which indicates milliamps .

If that is correct, the first plot shows 0 to 11mA scaling,? Post #11

So the plots are around 0.5mA

E

Attachments

-

12.4 KB Views: 10

-

12.2 KB Views: 10

- I used the same model posted by @eetech00 in post #10:

.MODEL J2N5457 NJF(Beta=0.150m Betatce=-500m Rd=1 Rs=1

+ Lambda=2.3m Vto=-2.572 Vtotc=-2.5m Is=181.3f Isr=1.747p

+ N=1 Nr=2 Xti=3 Alpha=2.543u Vk=152.2 Cgd=4p M=311.4m

+ Pb=500m Fc=500m Cgs=4.627p Kf=1.045e-002f Af=1)

The drain curve I got in proteus is: for Vgs from 0V to -1V, Vds from 0 to 25V and Id is 0.4mA for Vgs=0.

- which is same as @ericgibbs post 13

- while @ericgibbs on post #14 shows

which matches with @eetech00 graph in post #10 which shows 1mA at the top(but don't know what is Vgs for this curve).

But @ericgibbs circuit shows positive supply to the gate, I don't know whether it is due to this reason the drain curve is showing 1mA instead of 0.4uA for Vgs=0 and maybe @eetech00 is also using positive gate bias.

Because when I use positive gate bias I also get the similar curve as shown below,

But a JFET(n-channel) on a drain curve has max current Idss when Vgs=0V and negative bias Vgs is only applicable.

So what is going on here? is proteus wrong or model wrong or have i mistake somehere?

.MODEL J2N5457 NJF(Beta=0.150m Betatce=-500m Rd=1 Rs=1

+ Lambda=2.3m Vto=-2.572 Vtotc=-2.5m Is=181.3f Isr=1.747p

+ N=1 Nr=2 Xti=3 Alpha=2.543u Vk=152.2 Cgd=4p M=311.4m

+ Pb=500m Fc=500m Cgs=4.627p Kf=1.045e-002f Af=1)

The drain curve I got in proteus is: for Vgs from 0V to -1V, Vds from 0 to 25V and Id is 0.4mA for Vgs=0.

- which is same as @ericgibbs post 13

- while @ericgibbs on post #14 shows

which matches with @eetech00 graph in post #10 which shows 1mA at the top(but don't know what is Vgs for this curve).

But @ericgibbs circuit shows positive supply to the gate, I don't know whether it is due to this reason the drain curve is showing 1mA instead of 0.4uA for Vgs=0 and maybe @eetech00 is also using positive gate bias.

Because when I use positive gate bias I also get the similar curve as shown below,

But a JFET(n-channel) on a drain curve has max current Idss when Vgs=0V and negative bias Vgs is only applicable.

So what is going on here? is proteus wrong or model wrong or have i mistake somehere?

Are you sure you've mapped the .subckt pins to the symbol correctly in the proteus library? Probably should recheck.- I used the same model posted by @eetech00 in post #10:

.MODEL J2N5457 NJF(Beta=0.150m Betatce=-500m Rd=1 Rs=1

+ Lambda=2.3m Vto=-2.572 Vtotc=-2.5m Is=181.3f Isr=1.747p

+ N=1 Nr=2 Xti=3 Alpha=2.543u Vk=152.2 Cgd=4p M=311.4m

+ Pb=500m Fc=500m Cgs=4.627p Kf=1.045e-002f Af=1)

The drain curve I got in proteus is: for Vgs from 0V to -1V, Vds from 0 to 25V and Id is 0.4mA for Vgs=0.

View attachment 256827

- which is same as @ericgibbs post 13

View attachment 256828

- while @ericgibbs on post #14 shows

View attachment 256829

which matches with @eetech00 graph in post #10 which shows 1mA at the top(but don't know what is Vgs for this curve).

View attachment 256830

But @ericgibbs circuit shows positive supply to the gate, I don't know whether it is due to this reason the drain curve is showing 1mA instead of 0.4uA for Vgs=0 and maybe @eetech00 is also using positive gate bias.

Because when I use positive gate bias I also get the similar curve as shown below,

View attachment 256831

But a JFET(n-channel) on a drain curve has max current Idss when Vgs=0V and negative bias Vgs is only applicable.

So what is going on here? is proteus wrong or model wrong or have i mistake somehere?

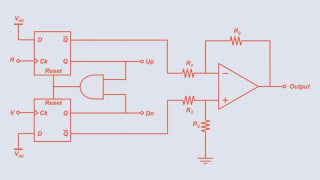

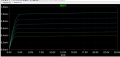

I am using 0v to -1v stepping on gate as is shown on the datasheet. You should be also.

In the graphic below, the top trace in each pane is the waveform at 0v vgs. The bottom trace is the waveform at -1v vgs.

You can see Id is at max (about 1ma) when vgs=0.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin