Hi everyone,

I'm working with Cadence Sigrity for PDN analysis, and I'm trying to understand the underlying SPICE syntax it auto-generates when importing a series-extracted capacitor .s2p file.

When I import my series model, Sigrity automatically generates the following subcircuit:

This node mapping is completely messing with my understanding of how a series component should be wired. Here is my thought process:

Am I misinterpreting how the S1 element maps its ports in this specific SPICE dialect? Does 1 2 3 2 mean something different here?

If my mapping assumption is correct, how does shorting Port 2 (V 3 2 0) and sharing the reference node accurately represent a 2-port series measurement mathematically to the solver?

Any insights into how the solver treats this syntax to extract the actual impedance would be highly appreciated!

I'm working with Cadence Sigrity for PDN analysis, and I'm trying to understand the underlying SPICE syntax it auto-generates when importing a series-extracted capacitor .s2p file.

When I import my series model, Sigrity automatically generates the following subcircuit:

Code:

*Series extracted s-parameter

.SUBCKT capacitor 1 2

S1 1 2 3 2

+ Model =capacitor_series.s2p

V 3 2 0

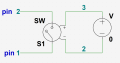

.ENDS- If the standard mapping for an N-port S-element in SPICE is (P1+ P1- P2+ P2-), then S1 1 2 3 2 implies:

- Port 1 is between nodes 1 and 2.

- Port 2 is between nodes 3 and 2.

- This means P1- and P2- share the same reference node (2).

- Then, the tool adds V 3 2 0, which is a 0V DC source. This effectively shorts node 3 to node 2.

- Consequently, it looks like P1-, P2+, and P2- are all short-circuited together!

Am I misinterpreting how the S1 element maps its ports in this specific SPICE dialect? Does 1 2 3 2 mean something different here?

If my mapping assumption is correct, how does shorting Port 2 (V 3 2 0) and sharing the reference node accurately represent a 2-port series measurement mathematically to the solver?

Any insights into how the solver treats this syntax to extract the actual impedance would be highly appreciated!

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin