Why does this prescaler says divide by 64 in the RF circuit diagram?

- Thread starter dante_clericuzzio

- Start date

Scroll to continue with content

Hello,

The MB506 consists of a couple of dividers.

One can select the dividing factor between 64, 128 and 256 times:

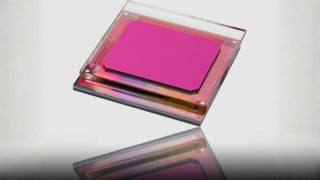

View attachment 135712

Thanks for the answer ...but i have further question why they need to divide in such preset scale?

Bertus

1) it's not practical to build frequency counter chipsets that run at GHz frequencies, they would be super expensive and power hungry, etc.

It's much easier to have a separate prescaler / divider block that brings the frequency down to a range that is practical for standard digital chips to handle. This way you can have low-cost frequency counters that can go up to GHz range.

2) The simplest way to implement this divider is with cascaded flip-flops that divide by 2, 4, 8 ,16, 32 etc. as you add more cascaded stages.

These are typically implemented in a super-fast logic family like ECL, GaAs, etc.

It's much easier to have a separate prescaler / divider block that brings the frequency down to a range that is practical for standard digital chips to handle. This way you can have low-cost frequency counters that can go up to GHz range.

2) The simplest way to implement this divider is with cascaded flip-flops that divide by 2, 4, 8 ,16, 32 etc. as you add more cascaded stages.

These are typically implemented in a super-fast logic family like ECL, GaAs, etc.

Actually i am not trying to build a frequency counter...but RF amplifier...If you don't mind would you like to share any RF amplifier circuit that could amplify up to 2.6 Ghz / 4G LTE? I have build one which work but i think its still below average and i would like to have it work at least at average or above average.1) it's not practical to build frequency counter chipsets that run at GHz frequencies, they would be super expensive and power hungry, etc.

It's much easier to have a separate prescaler / divider block that brings the frequency down to a range that is practical for standard digital chips to handle. This way you can have low-cost frequency counters that can go up to GHz range.

2) The simplest way to implement this divider is with cascaded flip-flops that divide by 2, 4, 8 ,16, 32 etc. as you add more cascaded stages.

These are typically implemented in a super-fast logic family like ECL, GaAs, etc.

Google; "MMIC".Actually i am not trying to build a frequency counter...but RF amplifier...If you don't mind would you like to share any RF amplifier circuit that could amplify up to 2.6 Ghz / 4G LTE? I have build one which work but i think its still below average and i would like to have it work at least at average or above average.

Thanks for the keyword ideaGoogle; "MMIC".

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin