Hi All,

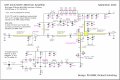

I succesfully designed and build RF driver amplifiers (up to 5W DATV) for VHF and UHF. I now started to do the same for SHF (and higher, 23cm and 13cm) so I looked around for examples and found many of them using wide PCB pads at the gate and drain, sometimes different sizes stacked after each other. Thus far I designed the impedance matching using the conjugate of the LDMOS fets published impedance data. Why is the approach different on higher frequenties I wonder. I know about stepped impedance transformers, how they operate but when do you start using them instead of regular striplines (CPW)? I'm attaching a picture showing the area of interest.

Thx for your kind help!

Richard (PA1RAM)

I succesfully designed and build RF driver amplifiers (up to 5W DATV) for VHF and UHF. I now started to do the same for SHF (and higher, 23cm and 13cm) so I looked around for examples and found many of them using wide PCB pads at the gate and drain, sometimes different sizes stacked after each other. Thus far I designed the impedance matching using the conjugate of the LDMOS fets published impedance data. Why is the approach different on higher frequenties I wonder. I know about stepped impedance transformers, how they operate but when do you start using them instead of regular striplines (CPW)? I'm attaching a picture showing the area of interest.

Thx for your kind help!

Richard (PA1RAM)

Attachments

-

497.7 KB Views: 26

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin