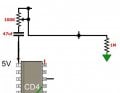

This is a followup to an old thread. The circuit provides a 24 volt DC pulse once a minute to a clock.

I built the circuit designed by @LowQCab and find that it's not working. The circuit is reproduced below with some annotations. I get a 6 Hz signal at pin 11 of CD1, but only if I disconnect pin 15 of CD1 AND if I hover my hand over the circuit or over parts of the power cord. Without the handwaving, there is no signal. I've checked connections as best I can but can't figure out what the problem is. Any suggestions appreciated.

I built the circuit designed by @LowQCab and find that it's not working. The circuit is reproduced below with some annotations. I get a 6 Hz signal at pin 11 of CD1, but only if I disconnect pin 15 of CD1 AND if I hover my hand over the circuit or over parts of the power cord. Without the handwaving, there is no signal. I've checked connections as best I can but can't figure out what the problem is. Any suggestions appreciated.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin