Hi,

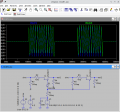

As discussed here one can add a pull-down resistor to the floating/outboard leg of a coupling capacitor to pull it to the negative rail. This is supposed to eliminate switching noise. The article states that, barring leakage, this outboard leg would normally be 0V. Is that true? Wouldn't that depend on the state of charge at the moment the cap got disconnected?

And why pull to the negative rail? The signal lives somewhere mid-rail. When the cap is switched in again it quickly needs to charge from 0V to ~4.5V. So why not pull this outboard leg to mid-rail?

As discussed here one can add a pull-down resistor to the floating/outboard leg of a coupling capacitor to pull it to the negative rail. This is supposed to eliminate switching noise. The article states that, barring leakage, this outboard leg would normally be 0V. Is that true? Wouldn't that depend on the state of charge at the moment the cap got disconnected?

And why pull to the negative rail? The signal lives somewhere mid-rail. When the cap is switched in again it quickly needs to charge from 0V to ~4.5V. So why not pull this outboard leg to mid-rail?

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin