Hi Everyone,

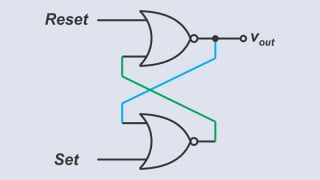

Can anybody explain why R/S flip flop is used in this circuit? I would also like to know how the clock signal should look like in duty cycle?

Last but not least, in R/S flip flop's truth table, it's stated that both set and reset pins shouldn't be turned to high state at the same time. That confuses me if they ever be turned to high in this circuitry. If so, can anybody explain why ?

Can anybody explain why R/S flip flop is used in this circuit? I would also like to know how the clock signal should look like in duty cycle?

Last but not least, in R/S flip flop's truth table, it's stated that both set and reset pins shouldn't be turned to high state at the same time. That confuses me if they ever be turned to high in this circuitry. If so, can anybody explain why ?

Attachments

-

205.5 KB Views: 19

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin