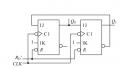

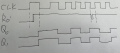

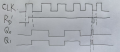

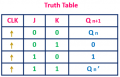

I encountered this question when leanring JK Flip-Flop.

MOD NOTE: Moved to Homework Help.

Can someone please explain how to do it?

MOD NOTE: Moved to Homework Help.

Last edited by a moderator:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin