Hello,

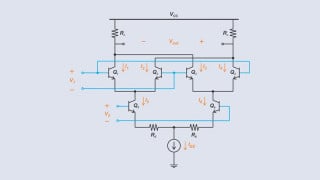

I have been working on designing a carrier board for a Seeed Studio XIAO microcontroller board. It is powered from a 5V source, and has on board 3V3 regulation. I have implemented a BSS138 level shifter (based on sparkfun/adafruit/NXP app note) for each pin to allow for full I/O compatibility at both 3V3 and 5V levels. I am designing in EasyEDA because I needed a free online solution for multiple devices.

I am hoping to get some feedback on the design before I go ahead and order the boards.

My biggest concerns would be the ground plane (bottom layer), the trace width, and general small mistakes that I may have made. I am inexperienced and have based this design off of similar online schematics.

Project link: https://oshwlab.com/stratos-ben/stratos-v2-board

Schematic:

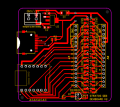

Top Layer Only:

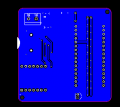

Top Layer Only: Bottom Layer Only:

Bottom Layer Only:

Thanks, I appreciate any help you can offer.

I have been working on designing a carrier board for a Seeed Studio XIAO microcontroller board. It is powered from a 5V source, and has on board 3V3 regulation. I have implemented a BSS138 level shifter (based on sparkfun/adafruit/NXP app note) for each pin to allow for full I/O compatibility at both 3V3 and 5V levels. I am designing in EasyEDA because I needed a free online solution for multiple devices.

I am hoping to get some feedback on the design before I go ahead and order the boards.

My biggest concerns would be the ground plane (bottom layer), the trace width, and general small mistakes that I may have made. I am inexperienced and have based this design off of similar online schematics.

Project link: https://oshwlab.com/stratos-ben/stratos-v2-board

Schematic:

Top Layer Only:

Top Layer Only: Bottom Layer Only:

Bottom Layer Only:

Thanks, I appreciate any help you can offer.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin