Hi everyone,

I am currently working on a high-power half-bridge converter project and would like to get some professional feedback on my gate driver stage design. I'm an Automation Engineering student at UNETI and this is my first time handling such high gate charges at this frequency.

Design Context:

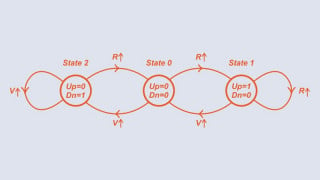

Here the schematic

Best regards,

Duong

I am currently working on a high-power half-bridge converter project and would like to get some professional feedback on my gate driver stage design. I'm an Automation Engineering student at UNETI and this is my first time handling such high gate charges at this frequency.

Design Context:

- Power Stage: Half-bridge configuration.

- MOSFETs: IRFP260N (TO-247) - Q_g approx 234nC to $240nC.

- Switching Frequency: 100kHz.

- Target Load: Approx. 1.2kW (Continuous current around 20A, peaking at 50A).

- Driver IC: UCC21520 (Isolated Dual-Channel).

- Isolation: Fully isolated control side (3.3V MCU logic).

- Bias Supply: Using B1212S-2W isolated DC-DC converters to provide a floating bias for each high-side and low-side switch.

- Drive Voltage: +15V for the gate-source voltage.

- Gate Drive Power Dissipation: At 100kHz and Q_g = 240nC, the calculated power dissipation inside the UCC21520 is nearing 0.7W - 1W. Given the small package, should I be worried about thermal runaway during extended operation?

- Buffer Stage: Would you recommend adding an external buffer (like the ZXGD3006 or a discrete Totem-pole) to offload the heat from the UCC21520 and ensure sharper switching edges?

- Floating Supply Stability: How reliable is the B1212S in a 100kHz environment? Should I add specific LC filtering to the output of these DC-DC modules to handle the high dv/dt transients at the switching nodes?

- Layout Advice: For 20A continuous operation, are there any pitfalls I should avoid regarding the Kelvin source connection and common-mode transient immunity (CMTI) for this IC?

Here the schematic

Best regards,

Duong

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin