I'm working on a hobby project and think I can harvest enough power from a slow, TTL level serial link. There are 5 data/control lines (all open collector) and a single ground. Signaling is the typical wired-or in open collector systems, each line relying on a 1k pullup to 5V.

Thinking through things, I figure I can harvest up to about 3mA from each line without affecting the operation of the link. With these being TLL level lines, pulling up to 3mA each, leads to a drop of 3V across the pullups, leaving the lines right about Vih for TTL. Realistically, I think I'd limit it to no more than 2.5mA, to keep things well above the 2V Vih level. With the 5 lines, plus sufficient capacitance, and a battery, I'm thinking I can easily ride through the transitions. They are all very slow. The maximum low time for any line is about 60us, and never are all of the lines low at the same time.

The idea then is to run each of the signal lines into a current limiter, then diode-or all of them into an LDO or SMPS to get down to the 1.8V I need for my microcontroller (uC). The uC subsystem sits about 10mA. With 5 lines, I can get 15mA when the bus is idle, and then ride through the transitions. I haven't completed all the math yet to determine how much backup power I need, but that will determine what kind of battery capacity I might need to meet long term operation.

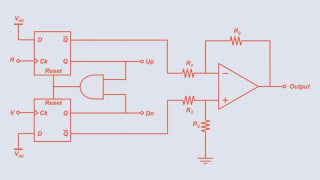

So, here's the crux of my question. I need to limit each line to about 2.5mA. I've been researching current limiters. I'm thinking I need high-side limiters since I have multiple power sources. A low-side limit wouldn't work as I need to limit from the source, not the overall current. I think. But I'm not finding any design principles on what architecture or how to select transistors or resistor values. Or are there IC's that do this? The ones I've found don't go down as low as 3mA, so I think I have to go with a discrete solution.

Further, how do I simulate this uC load? I'm not really finding much there. I saw one page model it has some capacitance and a current source in parallel. I guess I can sum all the bypass caps on the ICs and then put the maximum current draw I expect in the current source. But when I did so with some of the current limiters I considered, I couldn't keep the voltage high enough or there was excessive inrush current when it turned on.

So, I guess two questions:

1. Any references or assistance on designing current limiters down to about 2.5mA? I'm ok with a voltage drop so long as it stays above 1.8V.

2. How do I model the uC subystem's power requirements?

Thinking through things, I figure I can harvest up to about 3mA from each line without affecting the operation of the link. With these being TLL level lines, pulling up to 3mA each, leads to a drop of 3V across the pullups, leaving the lines right about Vih for TTL. Realistically, I think I'd limit it to no more than 2.5mA, to keep things well above the 2V Vih level. With the 5 lines, plus sufficient capacitance, and a battery, I'm thinking I can easily ride through the transitions. They are all very slow. The maximum low time for any line is about 60us, and never are all of the lines low at the same time.

The idea then is to run each of the signal lines into a current limiter, then diode-or all of them into an LDO or SMPS to get down to the 1.8V I need for my microcontroller (uC). The uC subsystem sits about 10mA. With 5 lines, I can get 15mA when the bus is idle, and then ride through the transitions. I haven't completed all the math yet to determine how much backup power I need, but that will determine what kind of battery capacity I might need to meet long term operation.

So, here's the crux of my question. I need to limit each line to about 2.5mA. I've been researching current limiters. I'm thinking I need high-side limiters since I have multiple power sources. A low-side limit wouldn't work as I need to limit from the source, not the overall current. I think. But I'm not finding any design principles on what architecture or how to select transistors or resistor values. Or are there IC's that do this? The ones I've found don't go down as low as 3mA, so I think I have to go with a discrete solution.

Further, how do I simulate this uC load? I'm not really finding much there. I saw one page model it has some capacitance and a current source in parallel. I guess I can sum all the bypass caps on the ICs and then put the maximum current draw I expect in the current source. But when I did so with some of the current limiters I considered, I couldn't keep the voltage high enough or there was excessive inrush current when it turned on.

So, I guess two questions:

1. Any references or assistance on designing current limiters down to about 2.5mA? I'm ok with a voltage drop so long as it stays above 1.8V.

2. How do I model the uC subystem's power requirements?

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin