Q. What are the number of stall cycles introduced by mispredicted branch instruction doing branch condition evaluation in EX stage in pipelined processor?

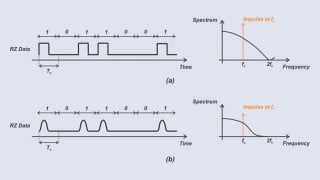

I was solving problems from chapter 4 in the book Computer Organization and Design by Patterson and Hannessey (4th edition). In one of the exercise, it says that the number of stall cycles introduced by mispredicted branch instruction doing branch condition evaluation in EX stage is 3. But I feel it should be 2:

So as you can see above, F and D of 2nd instruction is wasted beacause instruction 1 branch condition output was mispredicted. So shouldnt it be 2 stall cycles?

PS

I dont whether the question related to the instruction pipelining is on topic or not. Beg me pardon if I shouldnt be posting this on this site.

I was solving problems from chapter 4 in the book Computer Organization and Design by Patterson and Hannessey (4th edition). In one of the exercise, it says that the number of stall cycles introduced by mispredicted branch instruction doing branch condition evaluation in EX stage is 3. But I feel it should be 2:

So as you can see above, F and D of 2nd instruction is wasted beacause instruction 1 branch condition output was mispredicted. So shouldnt it be 2 stall cycles?

PS

I dont whether the question related to the instruction pipelining is on topic or not. Beg me pardon if I shouldnt be posting this on this site.

Attachments

-

4.8 KB Views: 2

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin