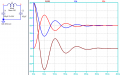

I want to devise an IC-based control for a simple circuit that equalises the voltage across two capacitors, so I can observe the behaviour of the inductor.

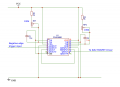

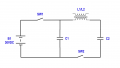

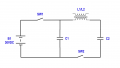

The sequence of events is this: SW1 is closed for a short while to charge up C1. SW1 is opened, and then SW2 is closed, so charge flows to C2 and the voltages equalise. This is the layout:

To be able to play around with the timings, I am devising a system where, as soon as SW1 is opened, by the falling edge of the external signal driving the MOSFET for the switch, there is then an adjustable delay before SW2 is closed. Once SW2 is closed, it remains so for an adjustable period (e.g. 0.1s) before opening, and the cycle repeats with SW1 closing when the external signal goes high for say 5% duty at 1Hz.

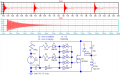

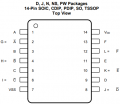

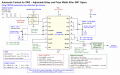

I asked AI to come up with a circuit based on a dual monostable that would do this, and it has produced what is in the next diagram, which is pretty rubbish, actually. So almost starting from scratch, I need to use a dual monostable to achieve the following sequence:

With reference to the first diagram, an external signal generator, operating at 1Hz and with a duty of 5% (i.e. an on time of 50ms) switches on SW1, comprising a driver and a MOSFET.

C1 charges up to the battery voltage and then, after SW1 reopens when the external signal goes low, I need an adjustable delay before SW2 (same driver and FET) closes for an adjustable period to allow the charge equalisation. The adjustable delay can be between 0.1 and 1.0s, and SW2 can be closed for between 0.05 and 0.5s.

Then the cycle starts again with the external signal closing SW1 again etc.

Any clarification and suggestions would be appreciated.

Thanks

The sequence of events is this: SW1 is closed for a short while to charge up C1. SW1 is opened, and then SW2 is closed, so charge flows to C2 and the voltages equalise. This is the layout:

To be able to play around with the timings, I am devising a system where, as soon as SW1 is opened, by the falling edge of the external signal driving the MOSFET for the switch, there is then an adjustable delay before SW2 is closed. Once SW2 is closed, it remains so for an adjustable period (e.g. 0.1s) before opening, and the cycle repeats with SW1 closing when the external signal goes high for say 5% duty at 1Hz.

I asked AI to come up with a circuit based on a dual monostable that would do this, and it has produced what is in the next diagram, which is pretty rubbish, actually. So almost starting from scratch, I need to use a dual monostable to achieve the following sequence:

With reference to the first diagram, an external signal generator, operating at 1Hz and with a duty of 5% (i.e. an on time of 50ms) switches on SW1, comprising a driver and a MOSFET.

C1 charges up to the battery voltage and then, after SW1 reopens when the external signal goes low, I need an adjustable delay before SW2 (same driver and FET) closes for an adjustable period to allow the charge equalisation. The adjustable delay can be between 0.1 and 1.0s, and SW2 can be closed for between 0.05 and 0.5s.

Then the cycle starts again with the external signal closing SW1 again etc.

Any clarification and suggestions would be appreciated.

Thanks

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin