Hello,

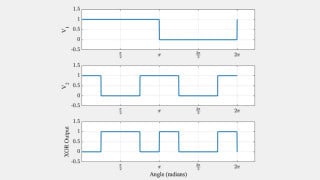

The block diagram is on the IC's datasheet. Let Vdd = 5V, and Vss = 0V. After the IC has been disabled (SD=high), I fed a square wave (5V/0V) to HIN pin. When the square wave is low, will this cause an ambiguous Q of the upper SR-flip flop? If so, will it ruin the operation of the IC?

About the pulse gen block, why do we have to have it? Will its upper and lower outputs be in-phase with the output of the upper NOR gate?

Thank You

BlackMelon

The block diagram is on the IC's datasheet. Let Vdd = 5V, and Vss = 0V. After the IC has been disabled (SD=high), I fed a square wave (5V/0V) to HIN pin. When the square wave is low, will this cause an ambiguous Q of the upper SR-flip flop? If so, will it ruin the operation of the IC?

About the pulse gen block, why do we have to have it? Will its upper and lower outputs be in-phase with the output of the upper NOR gate?

Thank You

BlackMelon

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin