MOD NOTE: Split from the following thread:

https://forum.allaboutcircuits.com/threads/input-circuit-for-a-0-to-30-mhz-frequency-counter.205374/

Can you elaborate more on the logic of frequency counting? I normally work with 16MHz to 20MHz MCUs, and would like to be able to count frequencies much higher, but it's escaping me as to how to make a circuit do it, that I can then input into the MCU. If this should be in a new thread, I apologizes, please let me know.

https://forum.allaboutcircuits.com/threads/input-circuit-for-a-0-to-30-mhz-frequency-counter.205374/

Dick,What kind of input circuit you need depends on what it is driving - the input of the CD4510 and 74HC7930 (switchable?)?

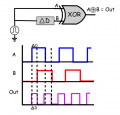

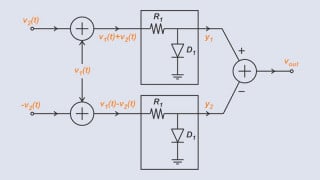

These might help:

To > 100 MHz:

View attachment 342377

To 30 MHz:

View attachment 342378

Can you elaborate more on the logic of frequency counting? I normally work with 16MHz to 20MHz MCUs, and would like to be able to count frequencies much higher, but it's escaping me as to how to make a circuit do it, that I can then input into the MCU. If this should be in a new thread, I apologizes, please let me know.

Last edited by a moderator:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin