Hello everyone,

I’m an RF engineer mostly working with passive RF components like filters, directional couplers, and so on. However, sometimes I need to build something simple using transistors.

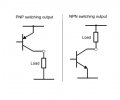

In my current project, I need to drive a GaN RF switch with logic levels of 0 / –28 V. I’m using a Zener-diode-based level-shifting technique to invert a 28 / 0 V logic signal into 0 / –28 V. After that, I assume I need a buffer stage to decouple the level shifter from the load.

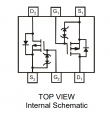

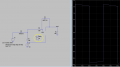

For this purpose, I picked a MOSFET DMP56D0UV with as low gate charge as I could find and built a circuit (attached as an LTSpice project). In the simulation, it works suspiciously well -- exactly how I want it to.

However, I have a few questions:

For example, to generate 28 / 0 V pulses, I use the IXDF604SIA driver IC. Would it be possible to invert VCC and GND, and apply a negative CMOS input signal (which is much easier to generate), and simply forget about the buffer stage? Or would that damage the chip?

Any help or insight would be greatly appreciated!

I’m an RF engineer mostly working with passive RF components like filters, directional couplers, and so on. However, sometimes I need to build something simple using transistors.

In my current project, I need to drive a GaN RF switch with logic levels of 0 / –28 V. I’m using a Zener-diode-based level-shifting technique to invert a 28 / 0 V logic signal into 0 / –28 V. After that, I assume I need a buffer stage to decouple the level shifter from the load.

For this purpose, I picked a MOSFET DMP56D0UV with as low gate charge as I could find and built a circuit (attached as an LTSpice project). In the simulation, it works suspiciously well -- exactly how I want it to.

However, I have a few questions:

- How much can I rely on the Zener diode to protect the MOSFET’s gate from breakdown? The datasheet gives a maximum Vgs of just 8 V.

- Will this circuit actually work in real life, or is it doomed to fail outside simulation?

- Are there any existing solutions that would save me from reinventing the wheel?

For example, to generate 28 / 0 V pulses, I use the IXDF604SIA driver IC. Would it be possible to invert VCC and GND, and apply a negative CMOS input signal (which is much easier to generate), and simply forget about the buffer stage? Or would that damage the chip?

Any help or insight would be greatly appreciated!

Attachments

-

1.9 KB Views: 10

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin