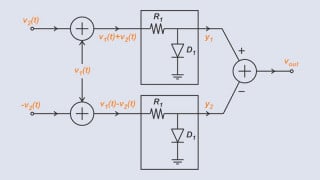

A counter needs to produce a 4-bit digital output representing decimal base numbers (5351619).

The sequence starts with the first digit on the left to the right and then when the output is the right digit it goes back to the first digit. We use a D Flip-Flop.

1- required to draw state diagram with letters referring to state and outputs remains in decimal format.

2 - required to convert diagram to state table.

Attached is a solution to the two questions. Can you comment on the correctness and kindly provide your advice.

Regards.

http://forum.allaboutcircuits.com/attachments/state_diagram_state_table-jpg.83824

The sequence starts with the first digit on the left to the right and then when the output is the right digit it goes back to the first digit. We use a D Flip-Flop.

1- required to draw state diagram with letters referring to state and outputs remains in decimal format.

2 - required to convert diagram to state table.

Attached is a solution to the two questions. Can you comment on the correctness and kindly provide your advice.

Regards.

http://forum.allaboutcircuits.com/attachments/state_diagram_state_table-jpg.83824

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin