Hi,

This is my first post here! I'm software engineer with some light experience in electronic engineering, mostly self-taught.

I am attempting to repair an old ADM-3A serial terminal. I've already repaired two, but this one is a real struggle. Using a logic analyzer I have been able to find a problem involving a JK flipflop (74LS113): http://freedatasheets.com/downloads/74LS113.pdf

So this flipflop has a functioning clock on pin 13, SET (pin 10) is always high, J (pin 11) is always high, and only K (pin 12) toggles between high and low. K is low if the terminal does not receive input (from an UART). This is the LOAD(1) operating mode for the flipflop, e.g. Q (pin 9) will be 1 and /Q (pin 8) will be 0. Now, when the terminal receives input, K will go high. Now as soon as the clock goes down, it should execute the TOGGLE operating mode, thus flipping Q to 0 and /Q to 1. However, this does not work as intended: /Q does always go to 1, but Q will generally stick at 1. Sometimes (let's say 1 in 5..10 times) Q will *very* briefly pulse to 0 at the same time /Q flips to 1, although the pulse is much shorter. Even weirder, when the clock goes back up again, /Q will always flip back to 0 again. AFAIK they both should only toggle at the next time the clock goes down (negative edge trigger).

Let me demonstrate this with a picture. Here is a screenshot from the logic analyzer that demonstrates the behavior. In this screenshot, INPUT is input K (pin 12), DOIT is /Q (pin 8). I have also connected pin 10 (SET) and 11 (J) that are always high but they are not labeled here. Clearly you can see here how /Q (DOIT) bounces back when the clock goes up again (which it shouldn't), and also that Q (/DOIT) doesn't even flip.

Luckily I also have a Known Good ADM-3A terminal so I can also show what SHOULD happen:

Note how DOIT and /DOIT are each other's opposites, as one would expect, and how they only change when the clock does down.

Ok, long story, but now here's my question: What could possibly cause this odd behavior on the broken ADM-3A? I have switched the flipflop from bad to good ADM-3A: it works there. Also, the flipflop from the good ADM-3A works in the bad ADM-3A, same exact symptoms. So that rules out a broken 74ls113 itself.

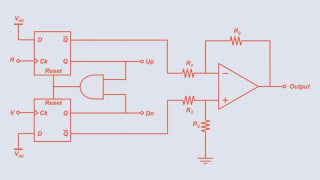

Could it be explained by output Q somehow tied high by another malfunctioning component in the circuit? Because it seems that /Q (DOIT) gets triggered correctly, but Q itself not so much, except for the occasional brief pulses (which seems worrysome). What else can I look at to debug this further?

This is my first post here! I'm software engineer with some light experience in electronic engineering, mostly self-taught.

I am attempting to repair an old ADM-3A serial terminal. I've already repaired two, but this one is a real struggle. Using a logic analyzer I have been able to find a problem involving a JK flipflop (74LS113): http://freedatasheets.com/downloads/74LS113.pdf

So this flipflop has a functioning clock on pin 13, SET (pin 10) is always high, J (pin 11) is always high, and only K (pin 12) toggles between high and low. K is low if the terminal does not receive input (from an UART). This is the LOAD(1) operating mode for the flipflop, e.g. Q (pin 9) will be 1 and /Q (pin 8) will be 0. Now, when the terminal receives input, K will go high. Now as soon as the clock goes down, it should execute the TOGGLE operating mode, thus flipping Q to 0 and /Q to 1. However, this does not work as intended: /Q does always go to 1, but Q will generally stick at 1. Sometimes (let's say 1 in 5..10 times) Q will *very* briefly pulse to 0 at the same time /Q flips to 1, although the pulse is much shorter. Even weirder, when the clock goes back up again, /Q will always flip back to 0 again. AFAIK they both should only toggle at the next time the clock goes down (negative edge trigger).

Let me demonstrate this with a picture. Here is a screenshot from the logic analyzer that demonstrates the behavior. In this screenshot, INPUT is input K (pin 12), DOIT is /Q (pin 8). I have also connected pin 10 (SET) and 11 (J) that are always high but they are not labeled here. Clearly you can see here how /Q (DOIT) bounces back when the clock goes up again (which it shouldn't), and also that Q (/DOIT) doesn't even flip.

Luckily I also have a Known Good ADM-3A terminal so I can also show what SHOULD happen:

Note how DOIT and /DOIT are each other's opposites, as one would expect, and how they only change when the clock does down.

Ok, long story, but now here's my question: What could possibly cause this odd behavior on the broken ADM-3A? I have switched the flipflop from bad to good ADM-3A: it works there. Also, the flipflop from the good ADM-3A works in the bad ADM-3A, same exact symptoms. So that rules out a broken 74ls113 itself.

Could it be explained by output Q somehow tied high by another malfunctioning component in the circuit? Because it seems that /Q (DOIT) gets triggered correctly, but Q itself not so much, except for the occasional brief pulses (which seems worrysome). What else can I look at to debug this further?

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin