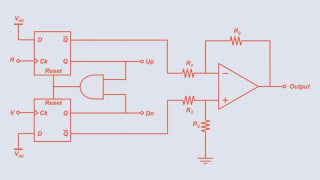

I wanted to use a circuit from an eval board which uses a 6V49205 clock generator which produces a HCSL output, but the input is LVDS. I have attached the section of the 6V49205 datasheet which describes the output clock:

The clock input is specified in this attached picture.

The eval board uses 50 ohm to ground termination on the output. I am having a hard time in seeing how this interface will work.

If you look at note 7 for the clock output it says the amplitude will be 1/2 of what is listed but the swing looks to be greater than the input can handle.

Output swing (max): 1150/2 - (-300/2) = 725mV, but the input says it can only handle a 600mV

Am I missing something here?

Thanks!

The clock input is specified in this attached picture.

The eval board uses 50 ohm to ground termination on the output. I am having a hard time in seeing how this interface will work.

If you look at note 7 for the clock output it says the amplitude will be 1/2 of what is listed but the swing looks to be greater than the input can handle.

Output swing (max): 1150/2 - (-300/2) = 725mV, but the input says it can only handle a 600mV

Am I missing something here?

Thanks!

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin