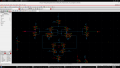

I have to design a double tail comparator for a 1GHz frequency and difference in voltage of 5mV. I should also do the pre and post layout simulation in 180nm. optimized your design for low delay. using Cadence Virtuoso.

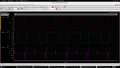

The problem I'm facing is one of the output(Outm) is correct and is able to sweep from 0V to1.8V, but not the other output (Outp).

How do i fix it whats wrong with my schematic?

How do I get Outp to negate and sweep from 0V to 1.8V?

MOD NOTE: Moved to Homework Help.

The problem I'm facing is one of the output(Outm) is correct and is able to sweep from 0V to1.8V, but not the other output (Outp).

How do i fix it whats wrong with my schematic?

How do I get Outp to negate and sweep from 0V to 1.8V?

MOD NOTE: Moved to Homework Help.

Attachments

-

159.8 KB Views: 11

-

185.6 KB Views: 10

Last edited by a moderator:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin