Hello!

The following is a kind of mental exercise that I am trying to solve.

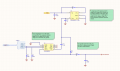

Let us assume that a circuit like the one below, where there is a power line powering a DCDC converter and a load. By load, I mean a generic complex circuit with computing power and so on. There is also a reset line whose only purpose is to carry a reset signal whenever the power to the load should be cut or restored. A dedicated switching circuit reads the reset signal and switches the power accordingly. Moreover, a LVDS line is connected to a LVDS to TTL converter to handle a serial communication between the load and the external world. Only the receiver part of the line is shown in the figure below.

Now assume that we want to get rid of the reset signal and that the power cannot be toggled at the origin. So the switch circuit must stay. To signal a reset we could imagine driving both the LVDS lines to a high impedance state. In such a case the switch circuit should detect this state and cut off the power. The power should be restored as soon as the LVDS lines go back to their normal common-mode voltage.

In other words, we would like to cut the power whenever the LVDS line is disconnected and restore the power when it is connected back.

Is that even possible? Could you point me in the correct direction for designing the switch circuit, please?

I have never seen something like this and googling "detect high impedance state" is not giving me anything very meaningful ...

Thank you

The following is a kind of mental exercise that I am trying to solve.

Let us assume that a circuit like the one below, where there is a power line powering a DCDC converter and a load. By load, I mean a generic complex circuit with computing power and so on. There is also a reset line whose only purpose is to carry a reset signal whenever the power to the load should be cut or restored. A dedicated switching circuit reads the reset signal and switches the power accordingly. Moreover, a LVDS line is connected to a LVDS to TTL converter to handle a serial communication between the load and the external world. Only the receiver part of the line is shown in the figure below.

Now assume that we want to get rid of the reset signal and that the power cannot be toggled at the origin. So the switch circuit must stay. To signal a reset we could imagine driving both the LVDS lines to a high impedance state. In such a case the switch circuit should detect this state and cut off the power. The power should be restored as soon as the LVDS lines go back to their normal common-mode voltage.

In other words, we would like to cut the power whenever the LVDS line is disconnected and restore the power when it is connected back.

Is that even possible? Could you point me in the correct direction for designing the switch circuit, please?

I have never seen something like this and googling "detect high impedance state" is not giving me anything very meaningful ...

Thank you

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin