Hello everyone,

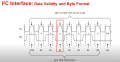

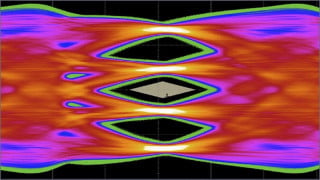

I'm trying to wrap my head around the concept of clock pulses, particularly in the context of SPI and I2C.

I understand that oscillators generate continuous square wave signals, but I'm a bit confused about clock pulses in the context of SPI and I2C.

I've come across terms like "set clock" "release clock." , "raising edge" and "failing edge"

How do these terms come into play with clock pulses, and what role do they serve in I2C clock signal?

I'm trying to wrap my head around the concept of clock pulses, particularly in the context of SPI and I2C.

I understand that oscillators generate continuous square wave signals, but I'm a bit confused about clock pulses in the context of SPI and I2C.

I've come across terms like "set clock" "release clock." , "raising edge" and "failing edge"

How do these terms come into play with clock pulses, and what role do they serve in I2C clock signal?

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin