I'm trying to get a clean sine wave output from a very simple voltage divider biasing for an NPN 2n3904 BJT.

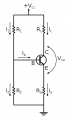

I set a Vcc = 10vdc. I selected the resistors (R1, R2, Re, Rc) to achieve a 5vdc midpoint bias at the collector, the 'Q' point when no AC signal is supplied to the base. So far so good, I verified with my DVM and with a scope that with no input to the base from my siggen, my collector is at about 5vdc, and the Vbe is about 0.7vdc. The transistor is on, and it is not saturated, it is at 5vdc on the collector, so the input sine wave (4vpp) should swing about a 5vdc level.

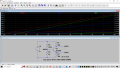

I turn on the siggen and get a clean sine wave at the base but a distorted (not clipped, just not a sine wave) output at the collector.

I am suspecting a bad 2N3904 NPN but before I buy new ones, was wondering if anyone knows of a fault of some kind that would lead a BJT to create a non-sine wave on the output. This is not a clipped output distortion at the collector - the signal looks like a positive 1/2 cycle with another, slightly higher voltage positive 1/2 cycle, then repeats that shape. Since the base is seeing a clean sine wave, and the collector Q point is 5vdc with 10v for Vcc, I'm not understanding why the midpoint biasing is failing to give me a clean sine wave output. I'm stumped.

My oscilloscope shows the correct frequency. I've tried frequencies from 1Khz to 1Mhz with no change: weird non-sine wave output.

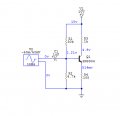

I've tried more than one value for Vcc and for the set of biasing resistors and I cannot get this BJT to produce a clean sine wave output.

I've tried using a blocking capacitor between the siggen and base, and without a blocking cap, no difference. The sine wave from the

siggen is perfect at the base, in both cases.

I set a Vcc = 10vdc. I selected the resistors (R1, R2, Re, Rc) to achieve a 5vdc midpoint bias at the collector, the 'Q' point when no AC signal is supplied to the base. So far so good, I verified with my DVM and with a scope that with no input to the base from my siggen, my collector is at about 5vdc, and the Vbe is about 0.7vdc. The transistor is on, and it is not saturated, it is at 5vdc on the collector, so the input sine wave (4vpp) should swing about a 5vdc level.

I turn on the siggen and get a clean sine wave at the base but a distorted (not clipped, just not a sine wave) output at the collector.

I am suspecting a bad 2N3904 NPN but before I buy new ones, was wondering if anyone knows of a fault of some kind that would lead a BJT to create a non-sine wave on the output. This is not a clipped output distortion at the collector - the signal looks like a positive 1/2 cycle with another, slightly higher voltage positive 1/2 cycle, then repeats that shape. Since the base is seeing a clean sine wave, and the collector Q point is 5vdc with 10v for Vcc, I'm not understanding why the midpoint biasing is failing to give me a clean sine wave output. I'm stumped.

My oscilloscope shows the correct frequency. I've tried frequencies from 1Khz to 1Mhz with no change: weird non-sine wave output.

I've tried more than one value for Vcc and for the set of biasing resistors and I cannot get this BJT to produce a clean sine wave output.

I've tried using a blocking capacitor between the siggen and base, and without a blocking cap, no difference. The sine wave from the

siggen is perfect at the base, in both cases.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin