I am working on an assignment and I am very confused with it.

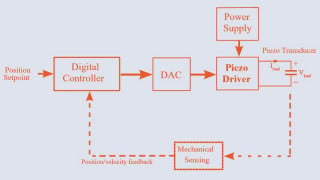

As far as I understand, a dynamic design will charge/discharge a load capacitor on the pre-charge phase (clock = LOW) and follow a desired design logic on the evaluation phase (clock = HIGH). This is achieved with the use of a PMOS transistor to read clock signal in pre-charge phase and NMOS transistors for the evaluation phase.

However, on my assignment, the clock is also part of the logic, and therefore the dynamic design is not as straight-forward as all the examples I have found and understood, where there we have a PMOS for the pre-charge phase and an NMOS system for the evaluation phase.

Here is the question:

I devised that the equation I am working with is Y = (A⊕B)⊕C

With the following truth table:

From the truth table above I singled out all the combinations that leads to Y = 0, to end with the following function (using ! to represent NOT):

!Y = !C(!A!B + AB) + C(!AB + A!B)

This will be the NMOS part of the design, or the evaluation part.

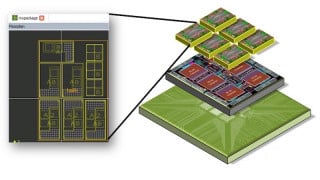

I then drew the schematic as follows:

However, I find myself questioning if this is the right design, given the lack of any PMOS transistors.

Please, any advise or resources would be great!

Cheers

As far as I understand, a dynamic design will charge/discharge a load capacitor on the pre-charge phase (clock = LOW) and follow a desired design logic on the evaluation phase (clock = HIGH). This is achieved with the use of a PMOS transistor to read clock signal in pre-charge phase and NMOS transistors for the evaluation phase.

However, on my assignment, the clock is also part of the logic, and therefore the dynamic design is not as straight-forward as all the examples I have found and understood, where there we have a PMOS for the pre-charge phase and an NMOS system for the evaluation phase.

Here is the question:

I devised that the equation I am working with is Y = (A⊕B)⊕C

With the following truth table:

From the truth table above I singled out all the combinations that leads to Y = 0, to end with the following function (using ! to represent NOT):

!Y = !C(!A!B + AB) + C(!AB + A!B)

This will be the NMOS part of the design, or the evaluation part.

I then drew the schematic as follows:

However, I find myself questioning if this is the right design, given the lack of any PMOS transistors.

Please, any advise or resources would be great!

Cheers

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin