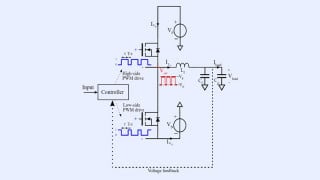

Hello, I am trying to design a 5V -> 3.3V buck converter as a design exercise and am implementing my own analog control circuit. At the moment I am not considering compensation or loop response as I am simply trying to regulate to the correct output before I consider the response and stability. Below is a photo of the control circuit, which to my understanding should be regulating to the target voltage. Note that Vfb is taken on the output from a 10k and 20k resistor divider, so should ideally be 2.178V when 3.3V is on the output. Additionally, the Vramp is a 600khz, 5V peak ramp wave. With the current loop seen below my output voltage is actually 1.27V. I am stuck at where this is going wrong and feel as though I have tried many different configurations. I have trouble thinking that a lack of compensator is causing this issue as the output is a pretty smooth 1.27V, only 2mV peak to peak.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin