Hi there.That is likely the result of the non-linearity of the FET resistance with signal voltage and polarity.

Try to keep the AC voltage at the FET drain to be no more than 10 mV peak or so to minimize such distortion.

Your design has about 200mV peak across the FET, if my calculations are correct.

So a change in the circuit would be required so that the FET voltage is lower (and preferably doesn't change significantly with input voltage).

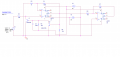

Here's an example design that keeps the FET voltage constant.

View attachment 123377

Yesterday i just searched "automatic gain control" circuit in this web site and i could finally found your schematic. I'm a new one here and I'm just curious about this circuit.

I have a pspice program for student. And I followed a schematic like your one.

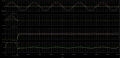

1. Why is the Vout amplitude always about 700mV even when changing the resistor values? was this your intention? Is there a way to change the amplitude of Vout?

2. Since the Veb of the BJT is constant as Vout, how does the collector voltage of the BJT (=Vgs of the JFET) change according to the amplitude of Vin?

3. Can you explain in detail about the feedback network of the BJT and RC circuit?

It's such a great design, but it's hard for me to understand. I appreciate your help.

Mod Edit :

Please don't Hijack other member's thread.

This thread was separated from here.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin