analyzing current limiting switch circuit

- Thread starter yef smith

- Start date

Scroll to continue with content

Ever use LTspice, the free circuit simulator? The learning curve is a little steep but once you learn it you'll have a great tool for answering this and many other questions. It's used by many here that can help you get it going.

@bertus beat me to it and gives the answer I almost did.

@bertus beat me to it and gives the answer I almost did.

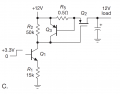

When the current through R5 generates a voltage of about 0.6-0.7V, Q3 starts to turn on, raising Q2's gate voltage.

This reduces Q2's gate-source voltage and when it approaches the Vgs(th) voltage, it will start turning off, limiting the load current.

Since you seem to have a lot of questions about various circuits you find, I also suggest you learn to use the free LTspice simulator from Analog Devices, so you can answer most of them yourself.

This reduces Q2's gate-source voltage and when it approaches the Vgs(th) voltage, it will start turning off, limiting the load current.

Since you seem to have a lot of questions about various circuits you find, I also suggest you learn to use the free LTspice simulator from Analog Devices, so you can answer most of them yourself.

Hello , few questions:

suppose Q1 is 2n2222A Q3 is 2n3906

1.When Vin=3.3V is there away to know if Q1 is lenear or saturated?

2.Yes Vbe of Q3 0.65V I=0.65/0.5=1.2A

How can we know if Q3 is saturated or not ?

Thanks.

https://www.onsemi.com/pdf/datasheet/p2n2222a-d.pdf

https://www.onsemi.com/download/data-sheet/pdf/2n3906-d.pdf

suppose Q1 is 2n2222A Q3 is 2n3906

1.When Vin=3.3V is there away to know if Q1 is lenear or saturated?

2.Yes Vbe of Q3 0.65V I=0.65/0.5=1.2A

How can we know if Q3 is saturated or not ?

Thanks.

https://www.onsemi.com/pdf/datasheet/p2n2222a-d.pdf

https://www.onsemi.com/download/data-sheet/pdf/2n3906-d.pdf

If you like doing math, you calculate the node voltages of the circuit at various load currents.How can we know if Q3 is saturated or not ?

I would just simulate the circuit.

It's a lot easier and likely will give more accurate results.

Last edited:

Hello crutschow,I want to lear how you see things and set the simulation properly.I have built the simulation attached.Q2 is a PMOS transistor it can be both saturated or linear, also the PNP and NPN.

what is intuition for each resistor R1 R3 R2 I'll know that each one of them is conducting properly?

Thanks.

When the current through R5 generates a voltage of about 0.6-0.7V, Q3 starts to turn on, raising Q2's gate voltage.

This reduces Q2's gate-source voltage and when it approaches the Vgs(th) voltage, it will start turning off, limiting the load current.

Since you seem to have a lot of questions about various circuits you find, I also suggest you learn to use the free LTspice simulator from Analog Devices, so you can answer most of them yourself.

what is intuition for each resistor R1 R3 R2 I'll know that each one of them is conducting properly?

Thanks.

When the current through R5 generates a voltage of about 0.6-0.7V, Q3 starts to turn on, raising Q2's gate voltage.

This reduces Q2's gate-source voltage and when it approaches the Vgs(th) voltage, it will start turning off, limiting the load current.

Since you seem to have a lot of questions about various circuits you find, I also suggest you learn to use the free LTspice simulator from Analog Devices, so you can answer most of them yourself.

Attachments

-

1.4 KB Views: 6

Attachments

-

1.8 KB Views: 2

Attachments

-

1.7 KB Views: 3

Hello Eric, I want to see the analog logic ,Why did you add Vr source.also could you say what is the logic behind shoosing R2 R1 R5 values?

Suppose we didnt have the exact values for R2 R1 and R5 what what you do in the simulation to find the exact values.

Thanks.

Suppose we didnt have the exact values for R2 R1 and R5 what what you do in the simulation to find the exact values.

Thanks.

schmitt trigger

- Joined Jul 12, 2010

- 2,056

Those famous Jim Williams’ electronic sculptures, which were also functional high performance circuits!

Hello , We have Q3 which is controlling the p-channel mosfet.

When Q3 is open then Vgate of the mofet is 12V and mosfet source is 12-0.7V(Vbe condition of Q3)

So Vsg of the mosfet will be -0.7V .

Three questions :

1. PMOS cannot open with Vsg -0.7 where is my logic wrong?

2.How can we know the Q3 will be open?

3.Do we need to use p-channel enhasment mode for this case?

When Q3 is open then Vgate of the mofet is 12V and mosfet source is 12-0.7V(Vbe condition of Q3)

So Vsg of the mosfet will be -0.7V .

Three questions :

1. PMOS cannot open with Vsg -0.7 where is my logic wrong?

2.How can we know the Q3 will be open?

3.Do we need to use p-channel enhasment mode for this case?

| Thread starter | Similar threads | Forum | Replies | Date |

|---|---|---|---|---|

| Y | analyzing pulse generating circuit | Analog & Mixed-Signal Design | 19 | |

|

|

Problem analyzing a resistor network | Homework Help | 19 | |

| C | Need Help Analyzing Silicon Structures in a IC | IC Design | 1 | |

| K | Analyzing Output [ SOLVED ] | Programming & Languages | 24 | |

| S | Analyzing Power from Current Source | Homework Help | 34 |

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin