Hello everyone,

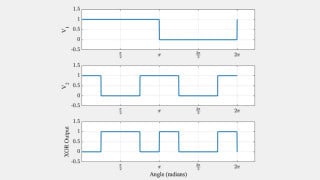

For my exam I have to design an amplifier to drive a 40nF capacitor. The signal is a trapezoidal wave that goes from 0 to 5V. Loop gain of my amplifier needs to be 8 from 0 to 200KHz. After a week I end up with the schematic in the picture.

However my output is not what i want even if my loop gain is almost 8. Moreover the system seems to be unstable, I tried to put a capacitor between base and collector of Q1, but doing this the output is broke down.

1) How can I reduce the delay in the output?

2) How can I make the amplifier stable?

Sorry for my english and thank you all for the answers.

For my exam I have to design an amplifier to drive a 40nF capacitor. The signal is a trapezoidal wave that goes from 0 to 5V. Loop gain of my amplifier needs to be 8 from 0 to 200KHz. After a week I end up with the schematic in the picture.

However my output is not what i want even if my loop gain is almost 8. Moreover the system seems to be unstable, I tried to put a capacitor between base and collector of Q1, but doing this the output is broke down.

1) How can I reduce the delay in the output?

2) How can I make the amplifier stable?

Sorry for my english and thank you all for the answers.

Attachments

-

29.7 KB Views: 40

-

35.1 KB Views: 43

-

48 KB Views: 44

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin