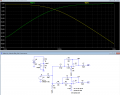

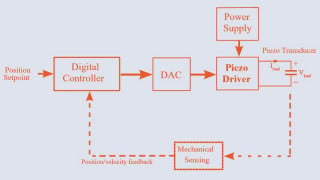

So I wanted to ask a question regarding this image here:

This was copied from the Linkwitz-Riley site.

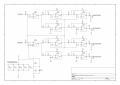

I am actually working on the 24/db version of this based on Rod Elliots work over at ESP Sound Products.

I also have been playing around w/ breadboarding a basic buffer, gain and inverting amp setup using a single-ended power supply based on "Professor Flore" here:

.

So far.. I understand all that.

But where I am unsure how to procede is regarding how to "adapt" the single supply topology into the LR filter. In the photo I provide above - the 23R7 and 68nF cap are tied to ground.

So here is my first question: when using the above filter in a single ended supply setup... would I need to create a new voltage divider similar to the video and tie these two points to that? I.E. A single "virtual ground" that all the typical "ground points" within the filter network can tie into?

Or are they left "floating" to infinity by adding a 100uF capacitor between their endpoint and the (-) voltage rail?

-Dean

This was copied from the Linkwitz-Riley site.

I am actually working on the 24/db version of this based on Rod Elliots work over at ESP Sound Products.

I also have been playing around w/ breadboarding a basic buffer, gain and inverting amp setup using a single-ended power supply based on "Professor Flore" here:

So far.. I understand all that.

But where I am unsure how to procede is regarding how to "adapt" the single supply topology into the LR filter. In the photo I provide above - the 23R7 and 68nF cap are tied to ground.

So here is my first question: when using the above filter in a single ended supply setup... would I need to create a new voltage divider similar to the video and tie these two points to that? I.E. A single "virtual ground" that all the typical "ground points" within the filter network can tie into?

Or are they left "floating" to infinity by adding a 100uF capacitor between their endpoint and the (-) voltage rail?

-Dean

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin